【FPGA零基础学习之旅#12】三线制数码管驱动(74HC595)串行移位寄存器驱动

🎉欢迎来到FPGA专栏~三线制数码管驱动

- ☆* o(≧▽≦)o *☆嗨~我是小夏与酒🍹

- ✨博客主页:小夏与酒的博客

- 🎈该系列文章专栏:FPGA学习之旅

- 文章作者技术和水平有限,如果文中出现错误,希望大家能指正🙏

- 📜 欢迎大家关注! ❤️

🎉 目录-三线制数码管驱动

- 一、效果演示

- 二、电路结构

- 三、代码详解

- 3.1 总体结构设计

- 3.2 驱动74HC595芯片

- 3.3 HEX8模块

- 3.4 顶层模块

- 四、按键控制改变数据值

一、效果演示

🥝ISSP调试演示:

程序配置完成:

调试:

🥝按键控制演示:

二、电路结构

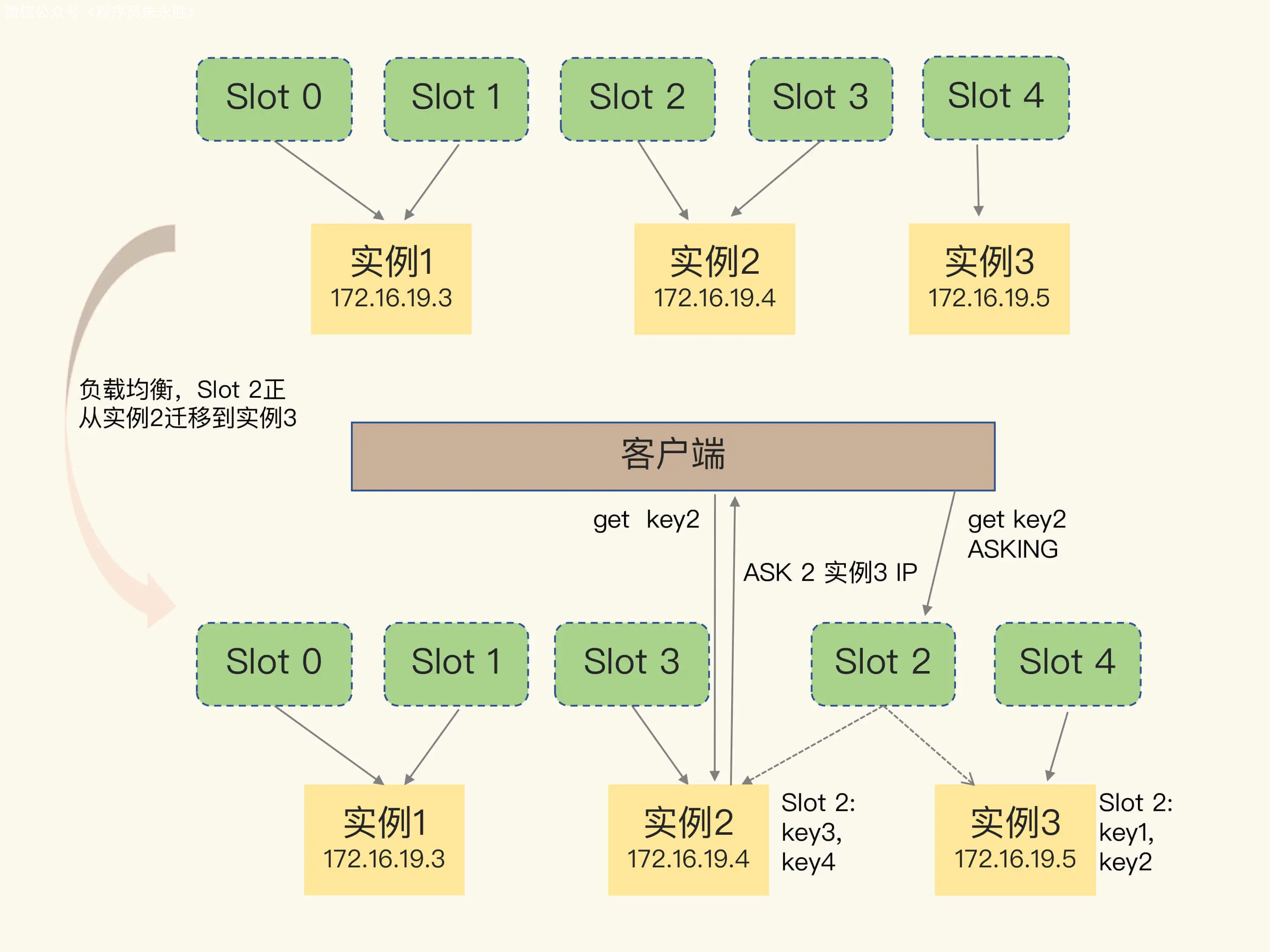

在三线制的数码管驱动中,使用74HC595芯片来减少FPGA的管脚数量使用。

关于74HC595芯片的介绍和时序图,参考文章:74HC595介绍 和 74HC595 驱动。

在AC620开发板上的数码管驱动电路:

AC620开发板使用的是74HC595芯片的级联来驱动显示:

三、代码详解

3.1 总体结构设计

先上RTL视图:

HEX8模块将seg和sel信号传给m74HC595_Driver模块,然后将接收到的信号转换为DS、SH_CP和ST_CP信号;ISSP模块用于调试。

3.2 驱动74HC595芯片

关于74HC595芯片的驱动,主要参考该时序图进行代码编写:

74HC595是8位串行移位寄存器,带有存储寄存器和三态寄存器,其中移位寄存器和存储寄存器分别采用不同的时钟。其可以把串行的信号转为并行的信号,因此常用做各种数码管以及点阵屏的驱动芯片。

该芯片的主要IO:

| IO名称 | 功能 |

|---|---|

| DS / SER | 串行数据输入端 |

| STCP / RCK | 存储寄存器的时钟输入。上升沿时移位寄存器中的数据进入存储寄存器,下降沿时存储寄存器中的数据保持不变。应用时通常将 ST_CP 置为低点平,移位结束后再在 ST_CP 端产生一个正脉冲更新显示数据。 |

| SHCP / SCK | 移位寄存器的时钟输入。上升沿时移位寄存器中的数据依次移动一位,即 Q0 中的数据移到 Q1 中,Q1 中的数据移到 Q2 中,依次类推;下降沿时移位寄存器中的数据保持不变。 |

由于在AC620开发板中芯片采用3.3V供电,这样在设计74HC595工作频率时,直接使用50M晶振四分频后的时钟作为其工作时钟。

74HC595的驱动代码,由于模块命名不能以数字开头,所以加了个m:

m74HC595_Driver.v:

module m74HC595_Driver(Clk,Rst_n,Data,S_EN,SH_CP,ST_CP,DS);parameter DATA_WIDTH = 16;input Clk;input Rst_n;input [DATA_WIDTH-1 : 0] Data; //data to sendinput S_EN; //send enoutput reg SH_CP; //shift clockoutput reg ST_CP; //latch data clockoutput reg DS; //shift serial dataparameter CNT_MAX = 4;reg [15:0] divider_cnt;//分频计数器wire sck_pluse;reg [4:0]SHCP_EDGE_CNT;//SH_CP EDGE counterreg [15:0]r_data;always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)r_data <= 16'd0;else if(S_EN)r_data <= Data;elser_data <= r_data;end//clock dividealways@(posedge Clk or negedge Rst_n)beginif(!Rst_n)divider_cnt <= 16'd0;else if(divider_cnt == CNT_MAX)divider_cnt <= 16'd0;elsedivider_cnt <= divider_cnt + 1'b1;endassign sck_pluse = (divider_cnt == CNT_MAX);always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)SHCP_EDGE_CNT <= 5'd0;else if(sck_pluse)beginif(SHCP_EDGE_CNT == 5'd31)SHCP_EDGE_CNT <= 5'd0;elseSHCP_EDGE_CNT <= SHCP_EDGE_CNT + 1'b1;endelseSHCP_EDGE_CNT <= SHCP_EDGE_CNT;end always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)beginSH_CP <= 1'b0;ST_CP <= 1'b0;DS <= 1'b0; endelse begincase(SHCP_EDGE_CNT)5'd0: begin SH_CP <= 1'b0; ST_CP <= 1'b1; DS <= r_data[15]; end5'd1: begin SH_CP <= 1'b1; ST_CP <= 1'b0;end5'd2: begin SH_CP <= 1'b0; DS <= r_data[14];end5'd3: begin SH_CP <= 1'b1; end5'd4: begin SH_CP <= 1'b0; DS <= r_data[13];end5'd5: begin SH_CP <= 1'b1; end5'd6: begin SH_CP <= 1'b0; DS <= r_data[12];end5'd7: begin SH_CP <= 1'b1; end5'd8: begin SH_CP <= 1'b0; DS <= r_data[11];end5'd9: begin SH_CP <= 1'b1; end5'd10:begin SH_CP <= 1'b0; DS <= r_data[10];end5'd11:begin SH_CP <= 1'b1; end5'd12:begin SH_CP <= 1'b0; DS <= r_data[9];end5'd13:begin SH_CP <= 1'b1; end5'd14:begin SH_CP <= 1'b0; DS <= r_data[8];end5'd15:begin SH_CP <= 1'b1; end5'd16:begin SH_CP <= 1'b0; DS <= r_data[7];end5'd17:begin SH_CP <= 1'b1; end5'd18:begin SH_CP <= 1'b0; DS <= r_data[6];end5'd19:begin SH_CP <= 1'b1; end5'd20:begin SH_CP <= 1'b0; DS <= r_data[5];end5'd21:begin SH_CP <= 1'b1; end5'd22:begin SH_CP <= 1'b0; DS <= r_data[4];end5'd23:begin SH_CP <= 1'b1; end5'd24:begin SH_CP <= 1'b0; DS <= r_data[3];end5'd25:begin SH_CP <= 1'b1; end5'd26:begin SH_CP <= 1'b0; DS <= r_data[2];end5'd27:begin SH_CP <= 1'b1; end5'd28:begin SH_CP <= 1'b0; DS <= r_data[1];end5'd29:begin SH_CP <= 1'b1; end5'd30:begin SH_CP <= 1'b0; DS <= r_data[0];end5'd31:begin SH_CP <= 1'b1; enddefault:begin SH_CP <= 1'b0;ST_CP <= 1'b0;DS <= 1'b0; endendcase endendendmoduleRTL视图:

3.3 HEX8模块

该模块的设计是在该文章的讲解基础之上进行修改:【FPGA零基础学习之旅#11】数码管动态扫描。

上述参考文章中的模块可以称为HEX6,驱动了6个数码管,在此我们需要驱动8个数码管,故可以将模块命名为HEX8。

需要注意的是,在设计数码管位选的时候,一定要看清使用板子的电路结构,弄清楚是高电平位选还是低电平位选!

HEX8.v:

module HEX8(input Clk, //50Minput Rst_n, //复位input En, //数码管显示使能input [31:0] disp_data, //8 × 4 = 32(8个数码管,数据格式为hex,总共输32位)output reg [7:0] seg, //数码管段选output [7:0] sel //数码管位选(数码管选择)

);reg [7:0]sel_r;//--------<分频器>--------reg [14:0]divider_cnt;//25000-1reg clk_1K;reg [3:0]data_tmp;//待显示数据缓存//1KHz分频计数器always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)divider_cnt <= 15'd0;else if(!En)divider_cnt <= 15'd0;else if(divider_cnt == 24999)divider_cnt <= 15'd0;elsedivider_cnt <= divider_cnt + 1'b1;end//1KHz扫描时钟always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)clk_1K <= 1'b0;else if(divider_cnt == 24999)clk_1K <= ~clk_1K;elseclk_1K <= clk_1K;end//--------<6位循环移位寄存器>-------- always@(posedge clk_1K or negedge Rst_n)beginif(!Rst_n)sel_r <= 8'b0000_0001;else if(sel_r == 8'b1000_0000)sel_r <= 8'b0000_0001;elsesel_r <= sel_r << 1;end //--------<6选1多路器>-------- always@(*)begincase(sel_r)8'b0000_0001:data_tmp = disp_data[3:0];8'b0000_0010:data_tmp = disp_data[7:4];8'b0000_0100:data_tmp = disp_data[11:8];8'b0000_1000:data_tmp = disp_data[15:12];8'b0001_0000:data_tmp = disp_data[19:16];8'b0010_0000:data_tmp = disp_data[23:20];8'b0100_0000:data_tmp = disp_data[27:24];8'b1000_0000:data_tmp = disp_data[31:28];default:data_tmp = 4'b0000;endcaseend//--------<LUT>-------- always@(*)begincase(data_tmp)4'h0:seg = 8'hc0;4'h1:seg = 8'hf9;4'h2:seg = 8'ha4;4'h3:seg = 8'hb0;4'h4:seg = 8'h99;4'h5:seg = 8'h92;4'h6:seg = 8'h82;4'h7:seg = 8'hf8;4'h8:seg = 8'h80;4'h9:seg = 8'h90;4'ha:seg = 8'h88;4'hb:seg = 8'h83;4'hc:seg = 8'hc6;4'hd:seg = 8'ha1;4'he:seg = 8'h86;4'hf:seg = 8'h8e;endcaseend//--------<2选1多路器>-------- assign sel = (En)?(sel_r):8'b1111_1111;endmodule3.4 顶层模块

在顶层模块中需要调用ISSP这样的一个IP核,操作过程和调试方法参考:【FPGA零基础学习之旅#11】数码管动态扫描。

smg.v:

module smg(input Clk, //50Minput Rst_n,//input [31:0] disp_data,output SH_CP, //shift clockoutput ST_CP, //latch data clockoutput DS //shift serial data

);wire [7:0] sel;//数码管位选(选择当前要显示的数码管)wire [7:0] seg;//数码管段选(当前要显示的内容) wire [31:0] disp_data;ISSP UISSP(.probe(),.source(disp_data));HEX8 UHEX8(.Clk(Clk),.Rst_n(Rst_n),.En(1'b1),.disp_data(disp_data),.sel(sel),.seg(seg));m74HC595_Driver Um74HC595_Driver(.Clk(Clk),.Rst_n(Rst_n),.Data({seg,sel}),.S_EN(1'b1),.SH_CP(SH_CP),.ST_CP(ST_CP),.DS(DS));endmodule四、按键控制改变数据值

项目要求: 通过控制按键,使得数码管显示不同的数据内容。

实现效果:

先看RTL视图来理解整体框架:

按下按键1,数码管显示12345678;按下按键2,数码管显示89abcdef。

按键消抖模块的设计参考该文章:【FPGA零基础学习之旅#10】按键消抖模块设计与验证(一段式状态机实现)。

在此贴出按键消抖的代码:

KeyFilter.v:

//

//模块:按键消抖模块

//key_state:输出消抖之后按键的状态

//key_flag:按键消抖结束时产生一个时钟周期的高电平脉冲

//

module KeyFilter(input Clk,input Rst_n,input key_in,output reg key_flag,output reg key_state

);//按键的四个状态localparamIDLE = 4'b0001,FILTER1 = 4'b0010,DOWN = 4'b0100,FILTER2 = 4'b1000;//状态寄存器reg [3:0] curr_st;//边沿检测输出上升沿或下降沿wire pedge;wire nedge;//计数寄存器reg [19:0]cnt;//使能计数寄存器reg en_cnt;//计数满标志信号reg cnt_full;//计数满寄存器//------<边沿检测电路的实现>------//边沿检测电路寄存器reg key_tmp0;reg key_tmp1;//边沿检测always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)beginkey_tmp0 <= 1'b0;key_tmp1 <= 1'b0;endelse beginkey_tmp0 <= key_in;key_tmp1 <= key_tmp0;end endassign nedge = (!key_tmp0) & (key_tmp1);assign pedge = (key_tmp0) & (!key_tmp1);//------<状态机主程序>------ //状态机主程序always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)begincurr_st <= IDLE;en_cnt <= 1'b0;key_flag <= 1'b0;key_state <= 1'b1;endelse begincase(curr_st)IDLE:beginkey_flag <= 1'b0;if(nedge)begincurr_st <= FILTER1;en_cnt <= 1'b1;endelsecurr_st <= IDLE;endFILTER1:beginif(cnt_full)beginkey_flag <= 1'b1;key_state <= 1'b0;curr_st <= DOWN;en_cnt <= 1'b0;end else if(pedge)begincurr_st <= IDLE;en_cnt <= 1'b0;endelsecurr_st <= FILTER1;endDOWN:beginkey_flag <= 1'b0;if(pedge)begincurr_st <= FILTER2;en_cnt <= 1'b1;endelsecurr_st <= DOWN;endFILTER2:beginif(cnt_full)beginkey_flag <= 1'b1;key_state <= 1'b1;curr_st <= IDLE;en_cnt <= 1'b0;end else if(nedge)begincurr_st <= DOWN;en_cnt <= 1'b0;endelsecurr_st <= FILTER2;enddefault:begincurr_st <= IDLE;en_cnt <= 1'b0;key_flag <= 1'b0;key_state <= 1'b1;endendcaseendend//------<20ms计数器>------ //20ms计数器//Clk 50_000_000Hz//一个时钟周期为20ns//需要计数20_000_000 / 20 = 1_000_000次always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)cnt <= 20'd0;else if(en_cnt)cnt <= cnt + 1'b1;elsecnt <= 20'd0;endalways@(posedge Clk or negedge Rst_n)beginif(!Rst_n)cnt_full <= 1'b0;else if(cnt == 999_999)cnt_full <= 1'b1;elsecnt_full <= 1'b0;endendmodule简单编写了一个KeyData模块用于不同数据的输入:

KeyData.v:

module KeyData(input Clk,input Rst_n,input Key_state1,input Key_flag1,input Key_state2,input Key_flag2,output reg [31:0] dis_data

);always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)dis_data <= 32'h00000000;else if(Key_flag1 && !Key_state1)dis_data <= 32'h12345678;else if(Key_flag2 && !Key_state2)dis_data <= 32'h89abcdef;else dis_data <= dis_data;endendmodule顶层模块KeyCtrlSmg.v:

module KeyCtrlSmg(input Clk,input Rst_n,input KeyIn1,input KeyIn2,output SH_CP, //shift clockoutput ST_CP, //latch data clockoutput DS //shift serial data

);wire key_state1;wire key_flag1;wire key_state2;wire key_flag2;wire [7:0] sel;//数码管位选(选择当前要显示的数码管)wire [7:0] seg;//数码管段选(当前要显示的内容) wire [31:0] dis_data;KeyFilter KeyFilter1(.Clk(Clk),.Rst_n(Rst_n),.key_in(KeyIn1),.key_flag(key_flag1),.key_state(key_state1));KeyFilter KeyFilter2(.Clk(Clk),.Rst_n(Rst_n),.key_in(KeyIn2),.key_flag(key_flag2),.key_state(key_state2));KeyData UKeyData(.Clk(Clk),.Rst_n(Rst_n),.Key_state1(key_state1),.Key_flag1(key_flag1),.Key_state2(key_state2),.Key_flag2(key_flag2),.dis_data(dis_data));HEX8 UHEX8(.Clk(Clk),.Rst_n(Rst_n),.En(1'b1),.disp_data(dis_data),.sel(sel),.seg(seg));m74HC595_Driver Um74HC595_Driver(.Clk(Clk),.Rst_n(Rst_n),.Data({seg,sel}),.S_EN(1'b1),.SH_CP(SH_CP),.ST_CP(ST_CP),.DS(DS));endmodule测试激励文件:

`timescale 1ns/1ns

`define clock_period 20module KeyCtrlSmg_tb;reg Clk;reg Rst_n;reg KeyIn1;reg KeyIn2;wire SH_CP;wire ST_CP;wire DS;KeyCtrlSmg UKeyCtrlSmg(.Clk(Clk),.Rst_n(Rst_n),.KeyIn1(KeyIn1),.KeyIn2(KeyIn2),.SH_CP(SH_CP), //shift clock.ST_CP(ST_CP), //latch data clock.DS(DS) //shift serial data);initial Clk = 1;always#(`clock_period / 2) Clk = ~Clk;initial begin Rst_n = 0;KeyIn1 = 1;KeyIn2 = 1;#200;Rst_n = 1;#200;KeyIn1 = 0;KeyIn2 = 1;#(`clock_period*10000)KeyIn1 = 1;KeyIn2 = 1;#(`clock_period*10000)KeyIn1 = 1;KeyIn2 = 0;#(`clock_period*10000)$stop;endendmodule仿真结果:

🧸结尾

- ❤️ 感谢您的支持和鼓励! 😊🙏

- 📜您可能感兴趣的内容:

- 【FPGA】串口通信讲解-状态机判断数据值

- 【Python】串口通信-与FPGA、蓝牙模块实现串口通信(Python+FPGA)

- 【Arduino TinyGo】【最新】使用Go语言编写Arduino-环境搭建和点亮LED灯

- 【全网首发开源教程】【Labview机器人仿真与控制】Labview与Solidworks多路支配关系-四足爬行机器人仿真与控制

相关文章:

【FPGA零基础学习之旅#12】三线制数码管驱动(74HC595)串行移位寄存器驱动

🎉欢迎来到FPGA专栏~三线制数码管驱动 ☆* o(≧▽≦)o *☆嗨~我是小夏与酒🍹 ✨博客主页:小夏与酒的博客 🎈该系列文章专栏:FPGA学习之旅 文章作者技术和水平有限,如果文中出现错误,希望大家能指…...

networkX-03-连通度、全局网络效率、局部网络效率、聚类系数计算

文章目录 1.连通度1.1 检查图是否连通1.2 检查有向图是否为强连通1.3 点连通度、边连通度: 2.网络效率2.1全局效率2.2 局部效率2.2.1 查找子图2.2.3 局部效率源码分析 3.聚类系数(Clustering Coefficient)3.1 聚类系统源码分析 教程仓库地址&…...

【深入解读Redis系列】Redis系列(五):切片集群详解

首发博客地址 https://blog.zysicyj.top/ 系列文章地址[1] 如果 Redis 内存很大怎么办? 假设一台 32G 内存的服务器部署了一个 Redis,内存占用了 25G,会发生什么? 此时最明显的表现是 Redis 的响应变慢,甚至非常慢。 这…...

无涯教程-JavaScript - NORMDIST函数

NORMDIST函数替代Excel 2010中的NORM.DIST函数。 描述 该函数返回指定均值和标准差的正态分布。此功能在统计中有非常广泛的应用,包括假设检验。 语法 NORMDIST(x,mean,standard_dev,cumulative)争论 Argument描述Required/OptionalXThe value for which you want the dis…...

递归应用判断是否循环引用

var data await _IDBInstance.DBOperation.QueryAsync<FormulaReference>(sql);//向上查询引用公式 List<FormulaReference> GetSonNode(long id, List<FormulaReference> nodeList, List<long> path null){if (path null){path new List<long…...

使用nginx-lua配置统一url自动跳转到hadoop-ha集群的active节点

下载安装nginx所用的依赖 yum -y install gcc zlib zlib-devel pcre-devel openssl openssl-devel下载nginx wget http://nginx.org/download/nginx-1.12.2.tar.gz tar -xvf nginx-1.12.2.tar.gz稍后安装nginx 安装lua语言 yum install readline-develcurl -R -O http://w…...

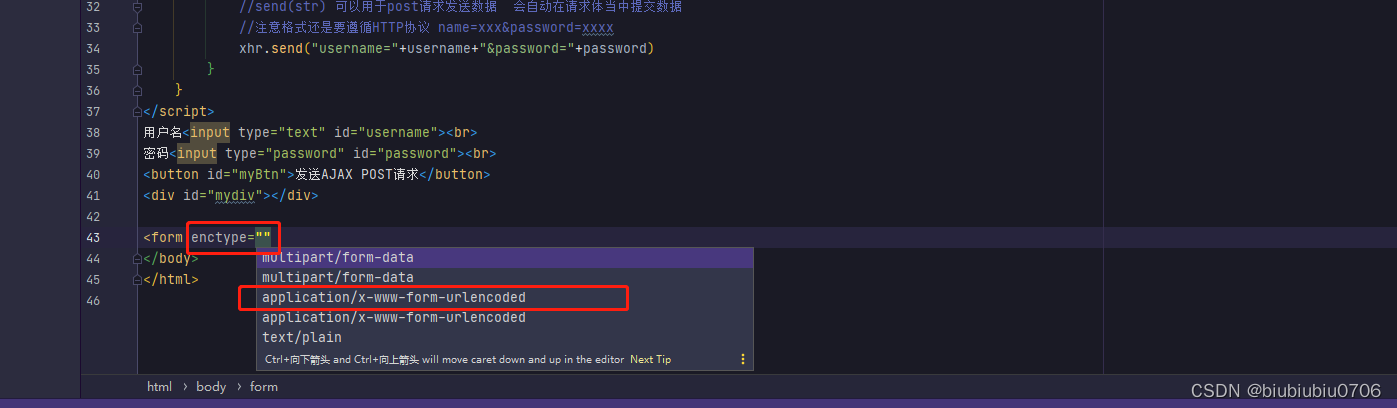

AJAX学习笔记2发送Post请求

AJAX学习笔记1发送Get请求_biubiubiu0706的博客-CSDN博客 继续 AJAX发送POST请求 无参数 测试 改回来 测试 AJAX POST请求 请求体中提交参数 测试 后端打断点 如何用AJAX模拟form表单post请求提交数据呢? 设置请求头必须在open之后,send之前 请求头里的设置好比…...

产品团队的需求分析指南

需求分析是软件开发流程中需求识别与管理的关键环节,需求分析的目的在于确保所有产品需求准确地代表了利益相关者的需求和要求。选择合适的需求分析方式可以帮助我们获取准确的产品需求,从而保证我们所交付的成果与利益相关者预期相符。 一、什么是需求…...

)

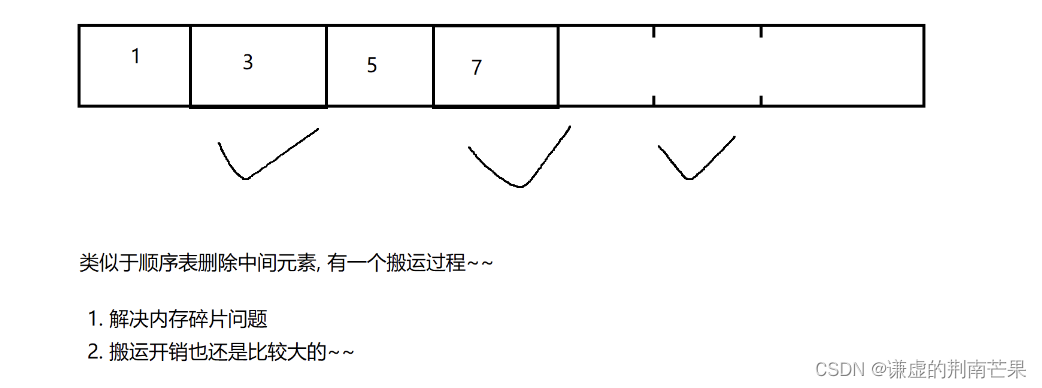

Python算法——排序算法(冒泡、选择、插入、快速、堆排序、并归排序、希尔、计数、桶排序、基数排序)

本文章只展示代码实现 ,原理大家可以参考: https://zhuanlan.zhihu.com/p/42586566 一、冒泡排序 def bubble_sort(lst):for i in range(len(lst) - 1): # 表示第i趟exchange False # 每一趟做标记for j in range(len(lst)-i-1): # 表示箭头if ls…...

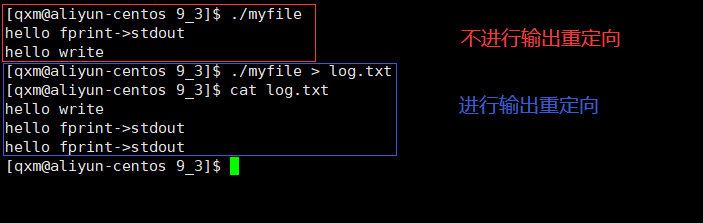

[Linux]文件描述符(万字详解)

[Linux]文件描述符 文章目录 [Linux]文件描述符文件系统接口open函数close函数write函数read函数系统接口与编程语言库函数的关系 文件描述符文件描述符的概念文件数据交换的原理理解“一切皆文件”进程默认文件描述符文件描述符和编程语言的关系 重定向输出重定向输入重定向追…...

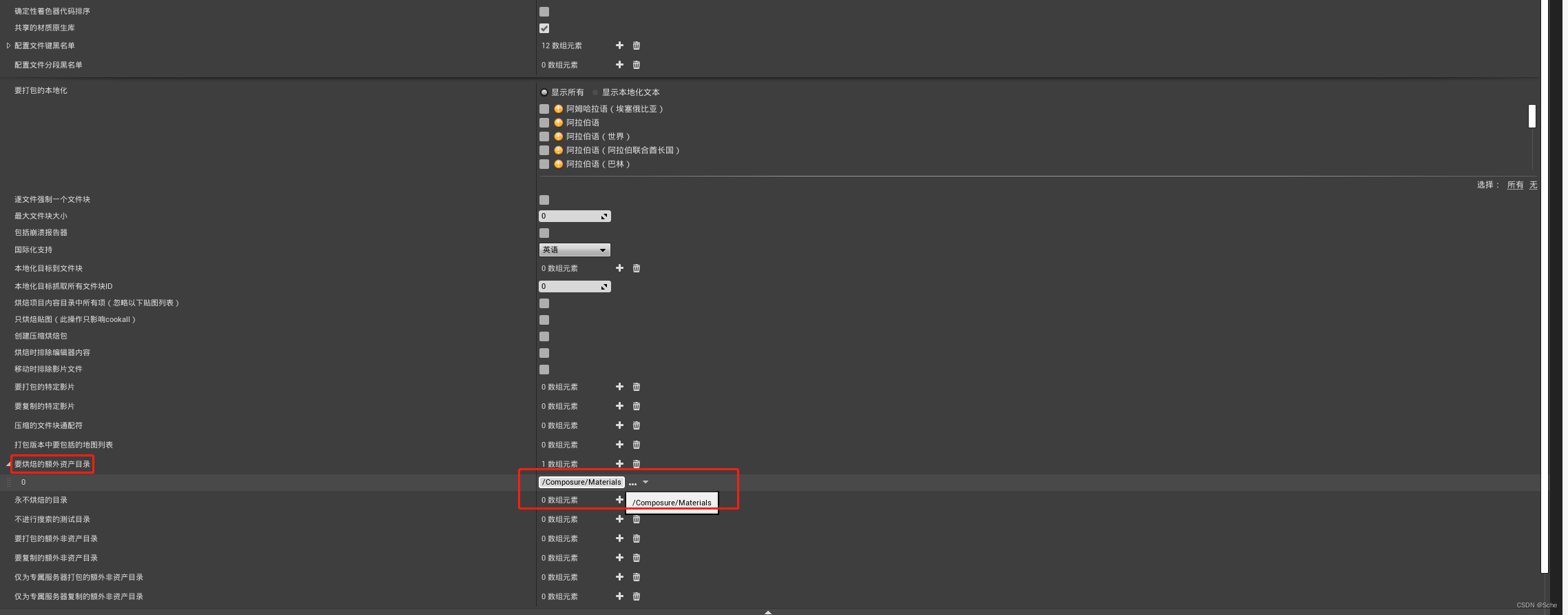

RenderTarget导出成图片,CineCamera相机

一、获取Cinecamera相机图像 1.1、启用UE自带插件 1.2、在UE编辑器窗口栏找到Composure合成,打开窗口 1. 3、右键空白处,新建合成,默认名称为 0010_comp;再右键新建的 0010_comp,新建图层元素 CGLayer层,默…...

深入探讨Java虚拟机(JVM):执行流程、内存管理和垃圾回收机制

目录 什么是JVM? JVM 执行流程 JVM 运行时数据区 堆(线程共享) Java虚拟机栈(线程私有) 什么是线程私有? 程序计数器(线程私有) 方法区(线程共享) JDK 1.8 元空…...

3D 碰撞检测

推荐:使用 NSDT场景编辑器快速搭建3D应用场景 轴对齐边界框 与 2D 碰撞检测一样,轴对齐边界框 (AABB) 是确定两个游戏实体是否重叠的最快算法。这包括将游戏实体包装在一个非旋转(因此轴对齐)的框中&#…...

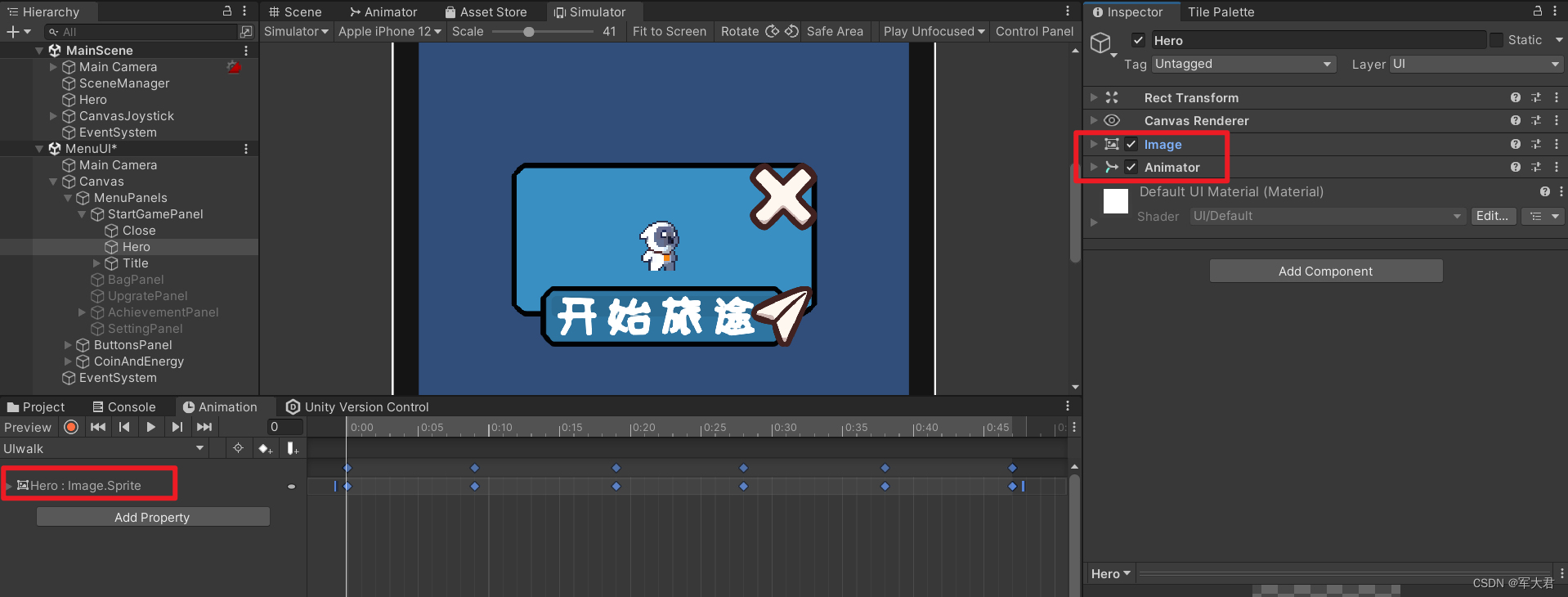

Unity Canvas动画不显示的问题

问题描述: 我通过角色创建了一个walk的动画,当我把这个动画给到Canvas里面的一个image上,这个动画就不能正常播放了,经过一系列的查看我才发现,canvas里面动画播放和非canvas得动画播放,他们的动画参数是不一样的。一个…...

NSSCTF2nd与羊城杯部分记录

文章目录 前言[NSSCTF 2nd]php签到[NSSCTF 2nd]MyBox[NSSCTF 2nd]MyHurricane[NSSCTF 2nd]MyJs[NSSCTF 2nd]MyAPK羊城杯[2023] D0nt pl4y g4m3!!!羊城杯[2023]ezyaml羊城杯[2023]Serpent羊城杯[2023]EZ_web羊城杯[2023]Ez_misc总结 前言 今天周日,有点无聊没事干&a…...

数据库(一) 基础知识

概述 数据库是按照数据结构来组织,存储和管理数据的仓库 数据模型 数据库系统的核心和基础是数据模型,数据模型是严格定义的一组概念的集合。因此数据模型一般由数据结构、数据操作和完整性约束三部分组成。数据模型主要分为三种:层次模型,网状模型和关…...

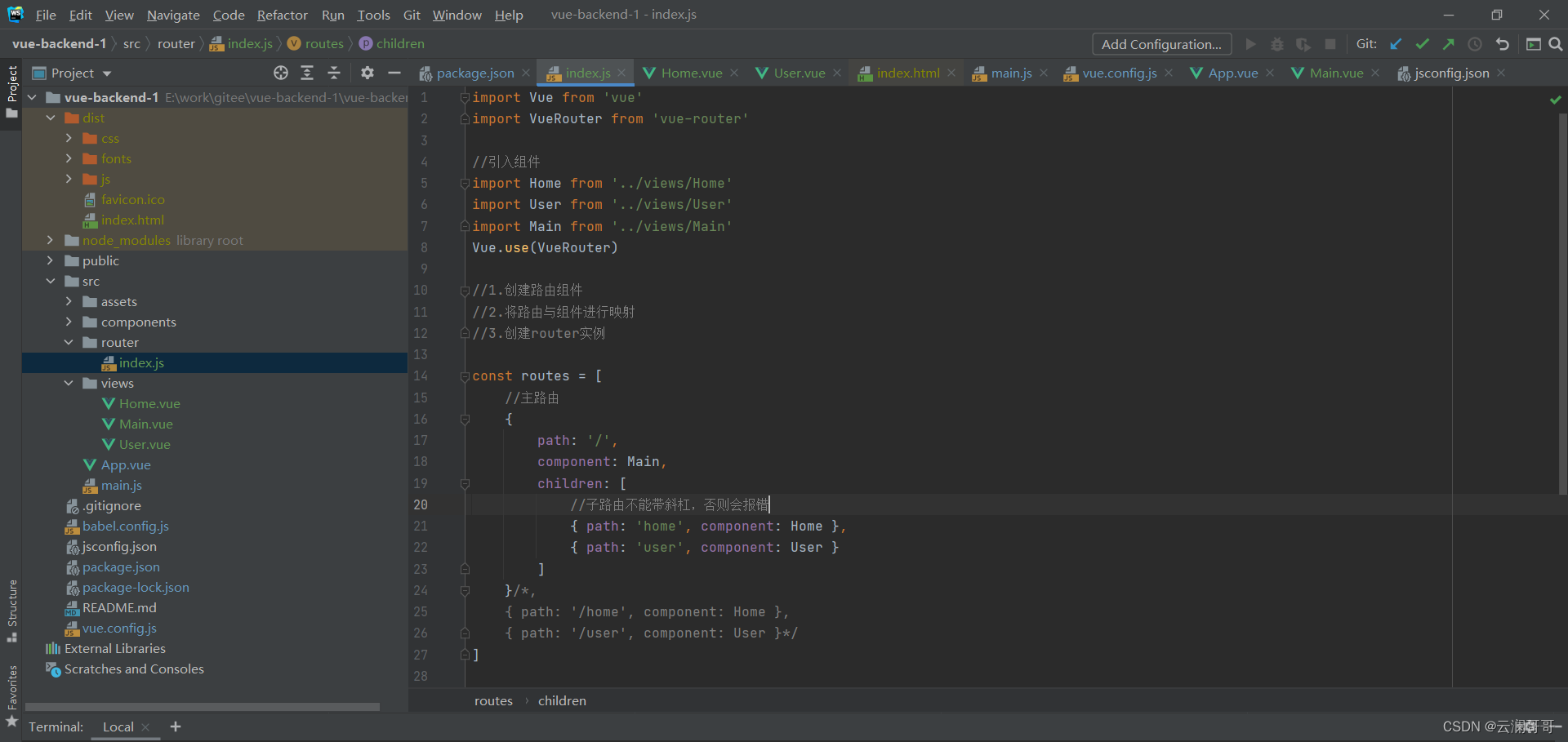

vue从零开始学习

npm install慢解决方法:删掉nodel_modules。 5.0.3:表示安装指定的5.0.3版本 ~5.0.3:表示安装5.0X中最新的版本 ^5.0.3: 表示安装5.x.x中最新的版本。 yarn的优点: 1.速度快,可以并行安装 2.安装版本统一 项目搭建: 安装nodejs查看node版本:node -v安装vue clie : np…...

dji uav建图导航系列(三)模拟建图、导航

前面博文【dji uav建图导航系列()建图】、【dji uav建图导航系列()导航】 使用真实无人机和挂载的激光雷达完成建图、导航的任务。 当需要验证某一个slam算法时,我们通常使用模拟环境进行测试,这里使用stageros进行模拟测试,实际就是通过模拟器,虚拟一个带有传感器(如…...

PixelSNAIL论文代码学习(1)——总体框架和平移实现因果卷积

文章目录 引言正文目录解析README.md阅读Setup配置Training the model训练模型Pretrained Model Check Point预训练的模型训练方法 train.py文件的阅读model.py文件阅读h12_noup_smallkey_spec模型定义_base_noup_smallkey_spec模型实现一、定义因果卷积过程通过平移实现因果卷…...

Python大数据处理利器之Pyspark详解

摘要: 在现代信息时代,数据是最宝贵的财富之一,如何处理和分析这些数据成为了关键。Python在数据处理方面表现得尤为突出。而pyspark作为一个强大的分布式计算框架,为大数据处理提供了一种高效的解决方案。本文将详细介绍pyspark…...

Cursor实现用excel数据填充word模版的方法

cursor主页:https://www.cursor.com/ 任务目标:把excel格式的数据里的单元格,按照某一个固定模版填充到word中 文章目录 注意事项逐步生成程序1. 确定格式2. 调试程序 注意事项 直接给一个excel文件和最终呈现的word文件的示例,…...

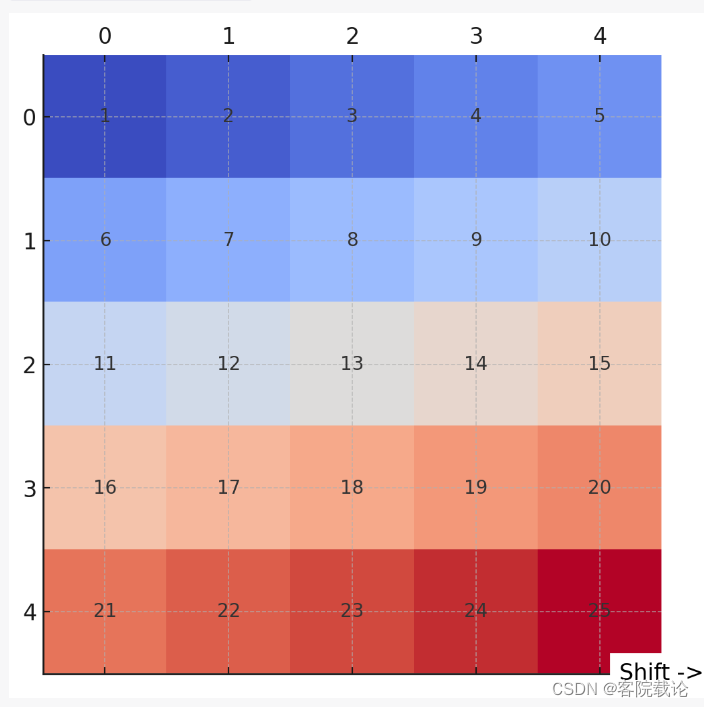

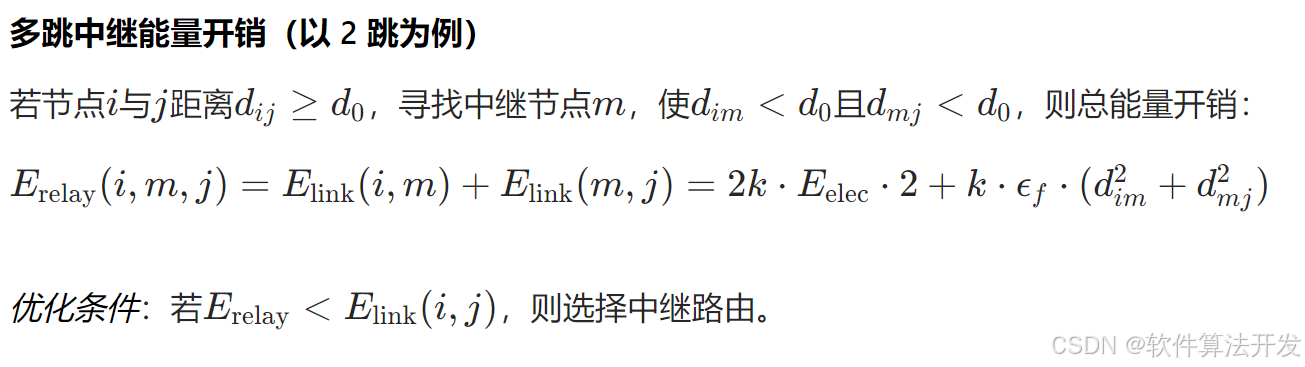

基于距离变化能量开销动态调整的WSN低功耗拓扑控制开销算法matlab仿真

目录 1.程序功能描述 2.测试软件版本以及运行结果展示 3.核心程序 4.算法仿真参数 5.算法理论概述 6.参考文献 7.完整程序 1.程序功能描述 通过动态调整节点通信的能量开销,平衡网络负载,延长WSN生命周期。具体通过建立基于距离的能量消耗模型&am…...

)

rknn优化教程(二)

文章目录 1. 前述2. 三方库的封装2.1 xrepo中的库2.2 xrepo之外的库2.2.1 opencv2.2.2 rknnrt2.2.3 spdlog 3. rknn_engine库 1. 前述 OK,开始写第二篇的内容了。这篇博客主要能写一下: 如何给一些三方库按照xmake方式进行封装,供调用如何按…...

React hook之useRef

React useRef 详解 useRef 是 React 提供的一个 Hook,用于在函数组件中创建可变的引用对象。它在 React 开发中有多种重要用途,下面我将全面详细地介绍它的特性和用法。 基本概念 1. 创建 ref const refContainer useRef(initialValue);initialValu…...

【解密LSTM、GRU如何解决传统RNN梯度消失问题】

解密LSTM与GRU:如何让RNN变得更聪明? 在深度学习的世界里,循环神经网络(RNN)以其卓越的序列数据处理能力广泛应用于自然语言处理、时间序列预测等领域。然而,传统RNN存在的一个严重问题——梯度消失&#…...

测试markdown--肇兴

day1: 1、去程:7:04 --11:32高铁 高铁右转上售票大厅2楼,穿过候车厅下一楼,上大巴车 ¥10/人 **2、到达:**12点多到达寨子,买门票,美团/抖音:¥78人 3、中饭&a…...

cf2117E

原题链接:https://codeforces.com/contest/2117/problem/E 题目背景: 给定两个数组a,b,可以执行多次以下操作:选择 i (1 < i < n - 1),并设置 或,也可以在执行上述操作前执行一次删除任意 和 。求…...

基础光照(Basic Lighting))

C++.OpenGL (10/64)基础光照(Basic Lighting)

基础光照(Basic Lighting) 冯氏光照模型(Phong Lighting Model) #mermaid-svg-GLdskXwWINxNGHso {font-family:"trebuchet ms",verdana,arial,sans-serif;font-size:16px;fill:#333;}#mermaid-svg-GLdskXwWINxNGHso .error-icon{fill:#552222;}#mermaid-svg-GLd…...

docker 部署发现spring.profiles.active 问题

报错: org.springframework.boot.context.config.InvalidConfigDataPropertyException: Property spring.profiles.active imported from location class path resource [application-test.yml] is invalid in a profile specific resource [origin: class path re…...

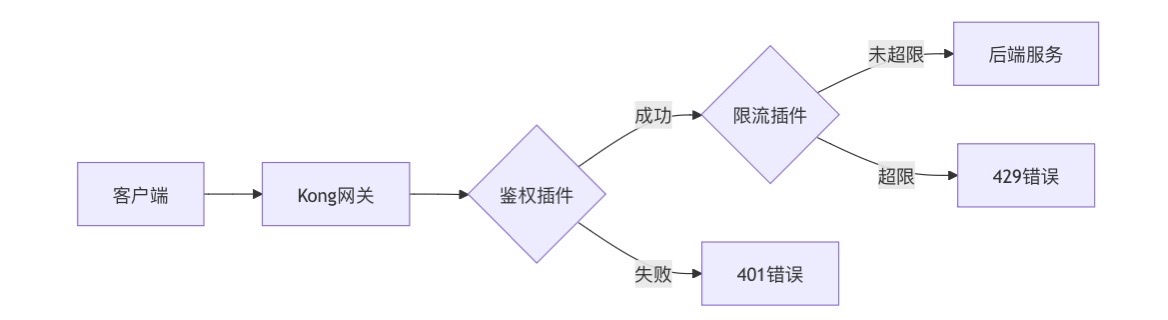

云原生安全实战:API网关Kong的鉴权与限流详解

🔥「炎码工坊」技术弹药已装填! 点击关注 → 解锁工业级干货【工具实测|项目避坑|源码燃烧指南】 一、基础概念 1. API网关(API Gateway) API网关是微服务架构中的核心组件,负责统一管理所有API的流量入口。它像一座…...