IC开发——VCS基本用法

1. 简介

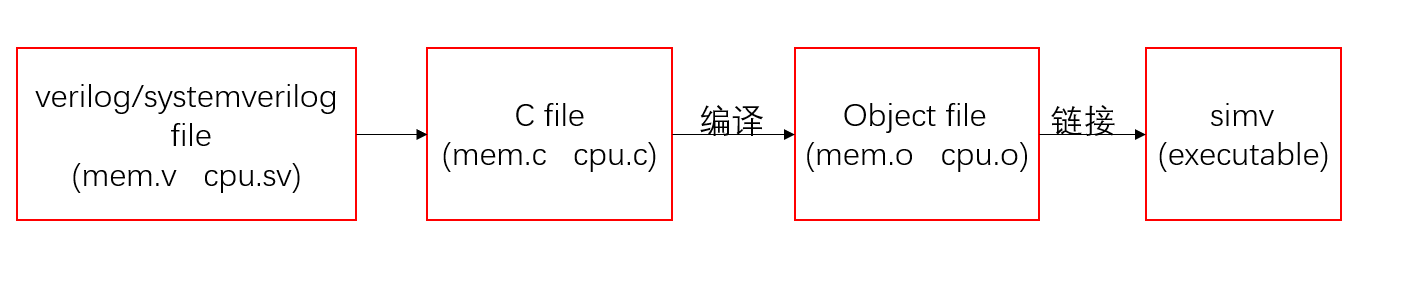

VCS是编译型verilog仿真器,处理verilog的源码过程如下:

VCS先将verilog/systemverilog文件转化为C文件,在linux下编译链接生成可执行文件,在linux下运行simv即可得到仿真结果。

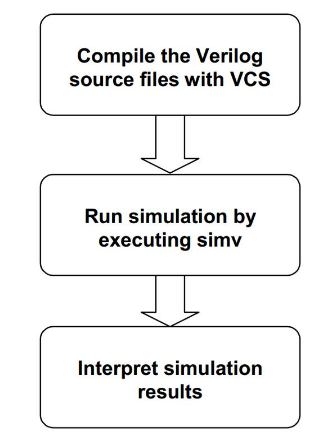

VCS使用步骤,先编译verilog源码,再运行可执行文件:

编译命令的格式:vcs sourcefile [compile_time_option] (编译选项用来控制编译过程)

执行仿真命令格式:./simv [run_time_option]

2. 示例

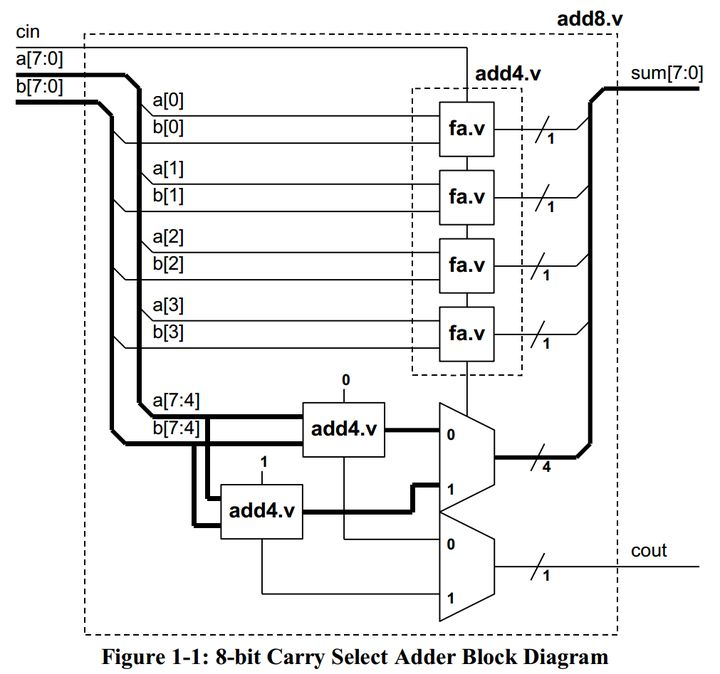

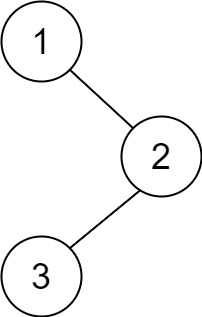

2.1. 电路结构图

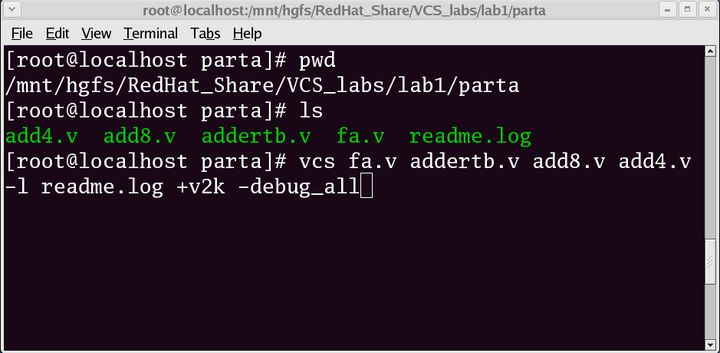

2.2. 编译

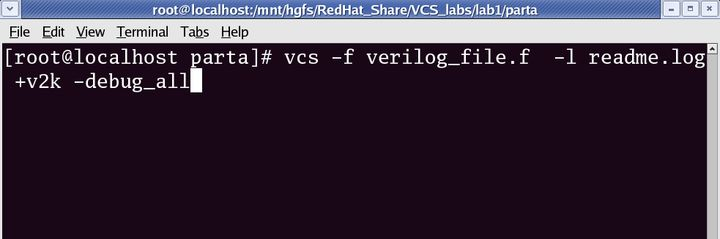

此电路为一位加法器 fa.v 组成4位加法器 add4.v,再组成一个8位加法器,使用资源换性能的思路,减小了行波进位加法器的进位延迟。顶层文件为add8.v,testbench为addertb.v。输入下图命令回车即可编译verilog文件,其中-l readme.log 用于将编译产生的信息放在log文件内,+v2k是使VCS兼容verilog 2001以前的标准。-debug_all用于产生debug所需的文件。

2.3. 仿真

./simv -l run.log 开始仿真,testbench里的$display打印仿真成功的信息,显示在终端上。使用-l run.log 记录终端上产生的信息。

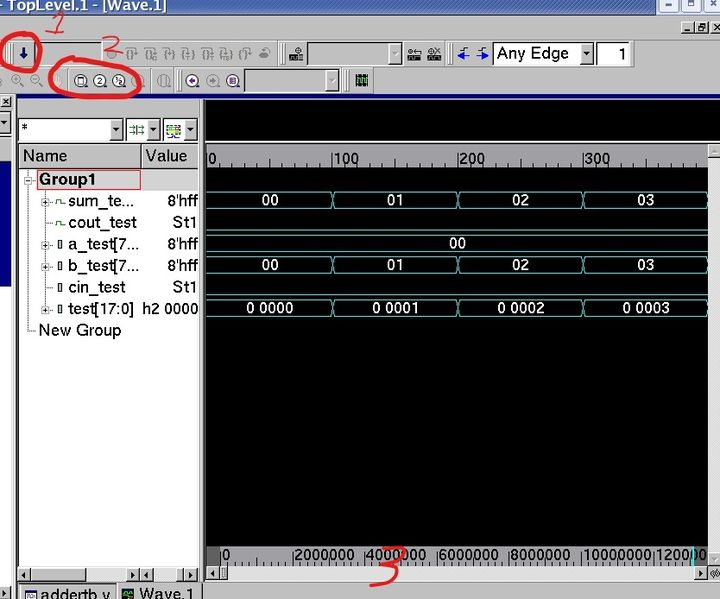

2.4. 添加波形信号

使用./simv -gui 命令打开图形化界面DVE,选中所有信号 --> 右键Add to Waves --> New Wave View

2.5. f文件

在工作目录下新建一个verilog_file.f文件,将所用到的verilog源码以及路径写入文件,并保存退出。使用-f verilog_file.f 选项,即可将.f文件里的源码全部编译。

2.6. 常用命令

以下有其他常用编译选项,注意各个编译选项的顺序,有时出错需要调整。

1) -R 编译后立即运行,即编译完成后立即执行 ./simv

2) -Mupdate 源文件有修改时,只要重新编译有改动的.v文件,节约编译时间。

3) -sverilog 打开对Systemverilog的支持,编译Systemverilog文件时使用。

4) -timescale=1ns/1ns 设置仿真精度

5) -o simv_file 编译默认产生的可执行文件为simv,可以使用 -o 更改可执行文件名。

2.7. makefile

命令比较多时,常用makefile文件来描述。

.PHONY:com sim cleanOUTPUT = adder_topVCS = vcs -sverilog +v2k -timescale=1ns/1ns \-debug_all \-o ${OUTPUT} \-l compile.log \SIM = ./${OUTPUT} -l run.logcom:${VCS} -f verilog_file.fsim:${SIM}clean:rm -rf ./csrc *.daidir *.log simv* *.key终端上输入 make com 后回车,相当于在终端中输入以下内容后回车,进行编译。

终端上输入make sim后回车进行仿真。

3. 代码覆盖率

3.1. 概念

在进行功能验证时,给设计添加激励信号,查看仿真结果,需要考虑覆盖率的问题。覆盖率分为代码覆盖率(code coverage)和功能覆盖率(function coverage)。功能覆盖率就是检查设计的功能是否完善,需要考虑很多不同的情况,是使用System verilog的重点内容。代码覆盖率是检查代码是否存在冗余,检查所有的代码是否都已经执行,状态机所有的状态是否都有到达,检查 if else 和 case 条件语句的条件是否都有使用。防止一些不必要的代码浪费芯片面积,毕竟面积就意味着钱。我们这里只讨论代码覆盖率。

对于RTL代码,通常考虑以下覆盖率:

-

Line coverage :行覆盖率,检查语句是否被执行。

-

Toggle coverage:检查电路的每个节点是否都有 0 -> 1 和 1 -> 0 的跳变。这种检查通常会使仿真变慢很多。

-

conditional coverage:检查条件语句是否覆盖了所有的情况。 比如有时写了if 语句,没有写else语句。

-

FSM coverage: 状态机覆盖率,检查状态机所有的状态是否都到达过。

-

path coverage:在always语句块和initial语句块中,有时会使用 if ... else 和 case 语句,在电路结构上便会产生一系列的数据路径。检查这些路径的覆盖情况。

3.2. 生成覆盖率文件

VCS在统计代码覆盖率的过程中,我们通常在编译和仿真命令上添加对应的开关选项,生成一个 .vdb文件记录覆盖率的情况。再使用dve打开该文件查看。下面介绍一些选项。

-cm <coveragetype> :打开对应类型的覆盖率,例如 -cm cond+tgl+lin+fsm+path为统计上述所有覆盖率。可根据需要增减。

-cm_name:设置记录有覆盖率信息文件的名字。

-cm_dir:指定生成文件的目录。

以上三个选项编译仿真过程都要加上。下面的选项在编译过程加上。

-cm_log + filename.log:.log文件记录仿真过程中统计覆盖率的信息。用的比较少。

-cm_nocasedef: 在统计case语句的条件覆盖率时,不考虑default条件未达到的情况。

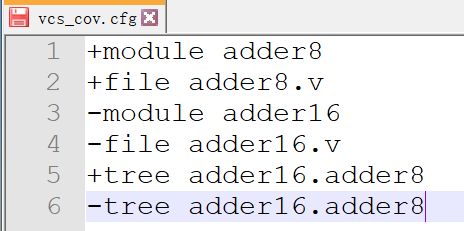

-cm_hier vcs_cov.cfg:通过.cfg文件(名字随便取)选择要查看覆盖率的模块/文件。

“+”代表查看,“-”代表不查看。tree代表查看某个模块调用的子模块。

在文件内部,可以使用特殊注释来打开和关闭代码覆盖率的统计:

//VCS coverage on 统计代码覆盖率

.......

//VCS coverage off 不统计代码覆盖率

在上述注释之间的内容,统计覆盖率。其余地方不统计。

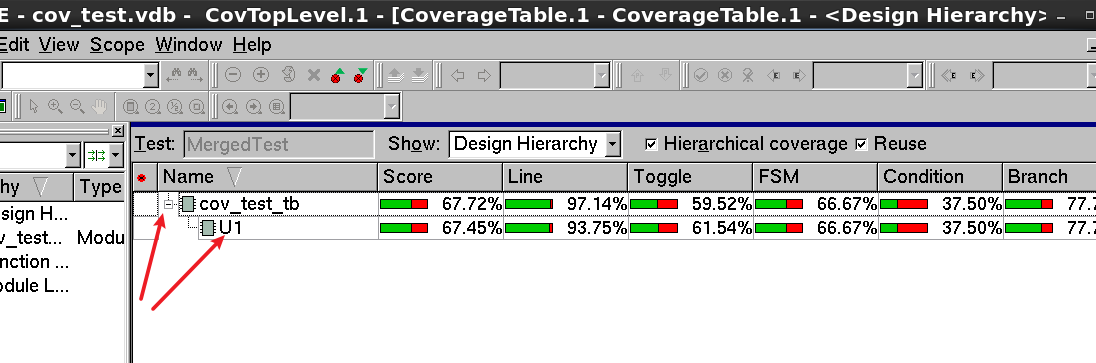

3.3. 查看覆盖

-

统计覆盖率命令并启动UI

dve -covdir *.vdb &-

单击箭头1处加号,再双击箭头2处的U1,查看设计的代码覆盖率。

-

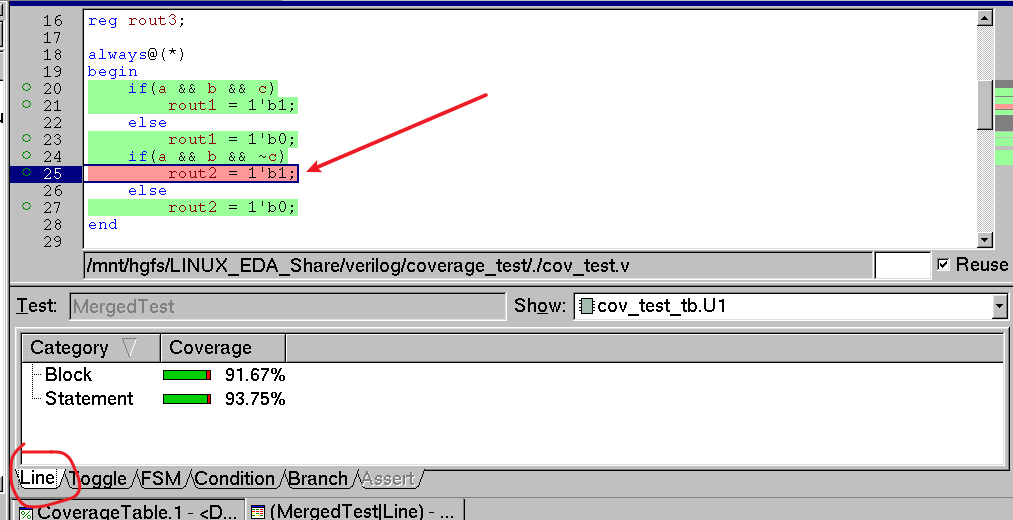

行覆盖率,第25行未执行过。

-

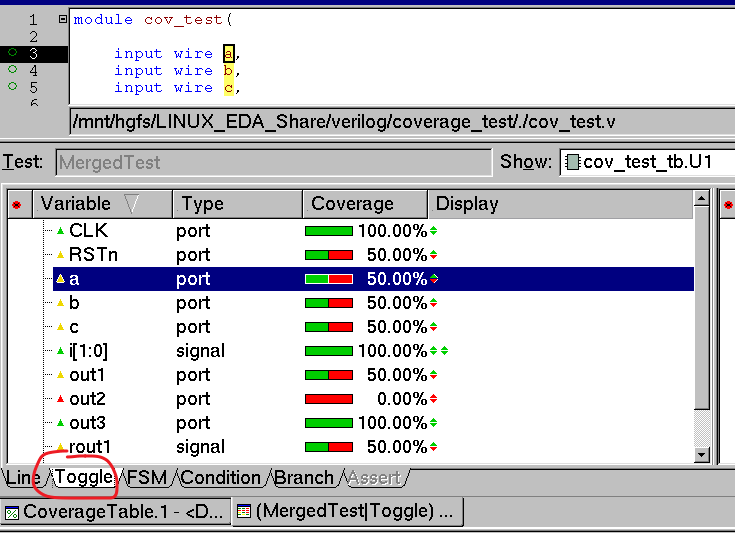

Toggle coverage:大量节点都没有 0 -> 1 和 1 -> 0 两种跳变

-

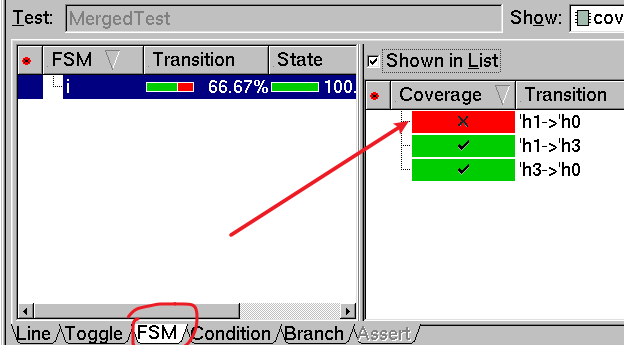

FSM coverage : 2'd1 -> 2'd0 的转换没有发生过。

-

condition 覆盖率

-

Branch(Path) 的覆盖率

4. 逻辑综合

当我们把所写的RTL进行的功能仿真通过之后,便输入到 Design Compiler工具中进行逻辑综合,逻辑综合的结果便是RTL代码转化为由与、或、非等门电路和触发器组成的电路,称为门级网表(netlist)。门级网表中便包含了电路的实际信息,例如逻辑门单元的扇入扇出系数,延迟等等。因此在逻辑综合完成之后,需要对网表再进行仿真验证,防止出现意想不到的错误。

对于实际电路,时钟信号并不是理想的“陡直”,门电路也存在延迟,这些电路的实际信息需要在逻辑综合的时候考虑到。RTL代码转换为门级电路,我们需要对电路施加一些约束。例如时序电路的工作频率,电路中组合逻辑块的延迟等等。综合工具会根据我们施加的约束做时序上的优化,从工艺库中挑选合适的单元,在面积,时序和功耗三个方面进行折中。当然满足时序的要求是首要的,面积和功耗要越小越好。

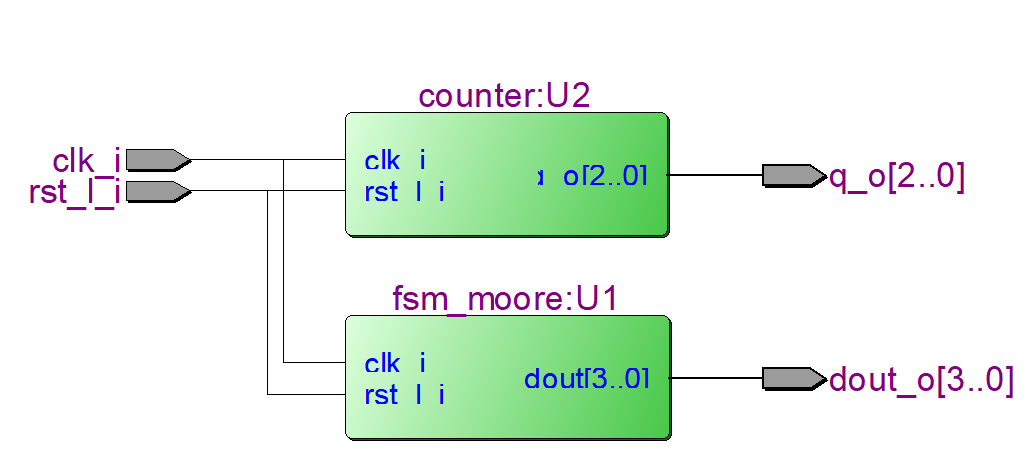

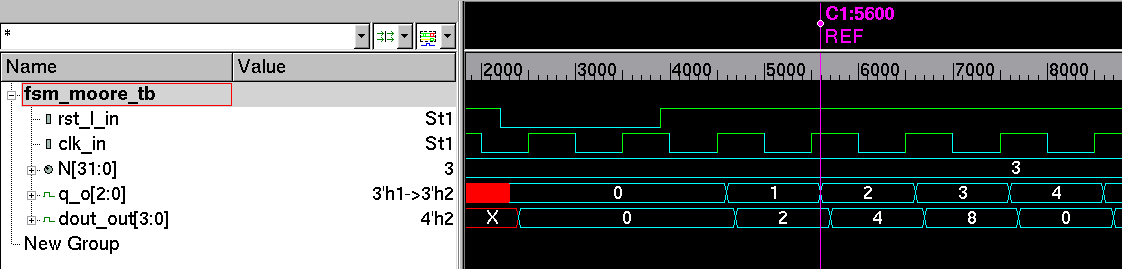

为简单起见,以一个Moore状态机为实例,做最基本的不添加约束的逻辑综合,用以生成门级仿真所需要的文件。设计电路框图如下:

由一个计数器和moore状态机组成。

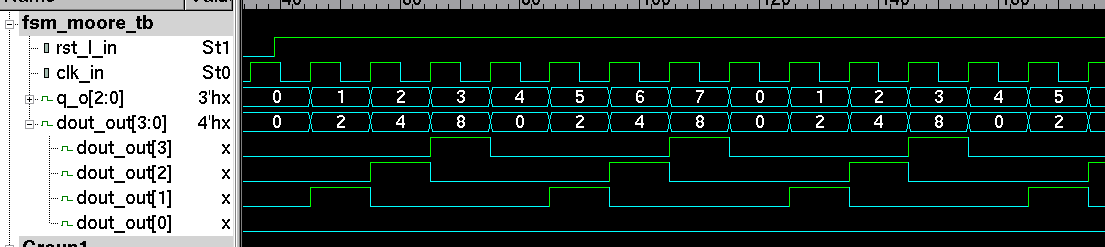

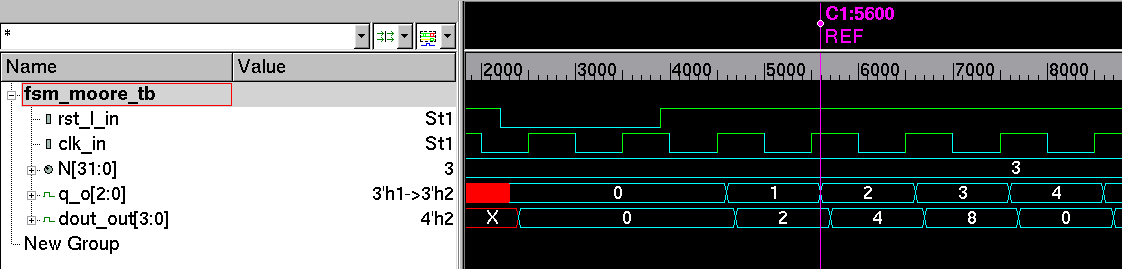

RTL仿真图如下

q_o 为三位计数器的输出,dout_out为状态机的输出,按 0000 0010 0100 1000 的顺序循环。

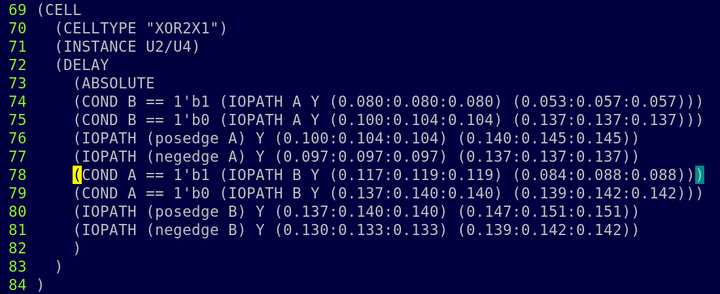

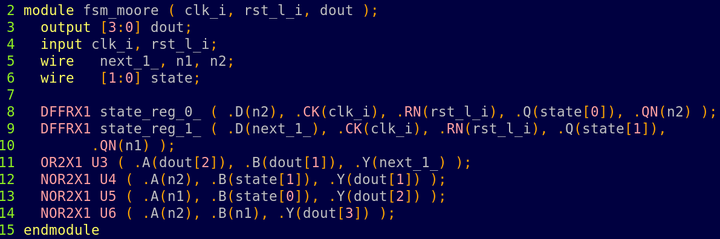

之后便在Design Compiler中进行综合生成后端和门级仿真的文件,我们在此关心VCS门级仿真所需要的文件。SDF文件包括设计中的时序信息,.v文件是以工艺库单元例化形成的verilog文件。

我们可以看到网表形式的verilog文件,由门电路和触发器例化组成。

4. 网表仿真

-

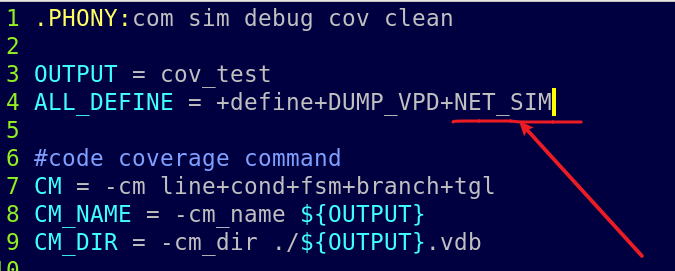

makefile模板添加了一个开关选项,由于网表.v文件是由工艺库单元例化的,工艺库中给出了一个verilog文件,包含各个单元。

-

定义NET_SIM这个宏。用于testbench中代码块的打开和关闭。

-

在Testbench中添加添加下面的代码块,使用sdf_annotate()系统函数将sdf文件“反标”到设计中,第一个参数指定sdf文件,第二个参数指定反标到哪一层的module上,这里我们选择顶层文件。其他参数保持默认即可

initial begin

`ifdef NET_SIM$sdf_annotate("/mnt/hgfs/LINUX_EDA_Share/DC_Projects/netlist_simulation/Top.sdf",Top,,,"TYPICAL","1:1:1","FROM_MTM");

`endif

end-

设置完毕后使用 make com sim debug 命令查看门级仿真波形,可以看到输出信号的跳变与时钟上升沿已有一段延迟,这与RTL仿真是不同的。

相关文章:

IC开发——VCS基本用法

1. 简介 VCS是编译型verilog仿真器,处理verilog的源码过程如下: VCS先将verilog/systemverilog文件转化为C文件,在linux下编译链接生成可执行文件,在linux下运行simv即可得到仿真结果。 VCS使用步骤,先编译verilog源…...

MongoDB~存储引擎了解

存储引擎 存储引擎是一个数据库的核心,主要负责内存、磁盘里数据的管理和维护。 MongoBD的优势,在于其数据模型定义的灵活性、以及可拓展性。但不要忽略,其存储引擎也是插件式的存在,支持不同类型的存储引擎,使用不同…...

JavaScript实现粒子数字倒计时效果附完整注释

<!DOCTYPE html> <html lang="en"><head><meta charset...

机制深度解析)

Dubbo SPI(Service Provider Interface)机制深度解析

Dubbo SPI(Service Provider Interface)机制是Apache Dubbo框架中一项核心的技术组件,它超越了传统Java SPI的范畴,为Dubbo带来了高度的可扩展性和灵活性。在分布式服务架构日益复杂多变的今天,Dubbo SPI机制通过巧妙的…...

常用中间件各版本下载

常用中间件下载地址 前言分布式中间件负载均衡中间件缓存中间件数据库中间件其他中间件1、Maven下载地址2、Git下载地址2、JDK下载地址3、MySQL下载地址4、Redis下载地址5、Nacos下载地址6、Tomcat下载地址7、Nginx下载地址8、RocketMQ下载地址8、RabbitMQ下载地址8、Erlang下载…...

VsCode SSH远程设置不用重复输入密码

winR输入cmd,回车,输入 C:\Users\Administrator> ssh-keygen -t rsa -b 4096 Generating public/private rsa key pair. Enter file in which to save the key (C:\Users\Administrator/.ssh/id_rsa): Enter passphrase (empty for no passphrase): …...

【Linux】:进程切换

朋友们、伙计们,我们又见面了,本期来给大家解读一下有关Linux进程切换的知识点,如果看完之后对你有一定的启发,那么请留下你的三连,祝大家心想事成! C 语 言 专 栏:C语言:从入门到精…...

MongoDB CRUD操作:删除文档

MongoDB CRUD操作:删除文档 文章目录 MongoDB CRUD操作:删除文档删除集合的所有文档删除符合条件的所有文件删除第一个符合条件的文档## 在MongoDB Atlas中删除文档删除行为索引 原子性写确认 可以使用下面的方式删除MongoDB集合的文档: 使用…...

SpringBoot集成腾讯COS流程

1.pom.xml中添加cos配置 <!--腾讯cos --> <dependency><groupId>com.qcloud</groupId><artifactId>cos_api</artifactId><version>5.6.28</version> </dependency> 2.application.yaml中添加cos配置 # 腾讯云存储cos…...

中高级前端开发岗

定位: 日常迭代任务的核心研发,具备高质、高效完成迭代任务的能力。 素质要求: 业务专家或擅长某一方向技术;有较丰富的开发经验;需要具备良好的沟通和协作能力,能够与其他部门和团队进行有效的沟通和协…...

idea常用配置

文章目录 I 常见问题1.1 取消maven忽略文件清单1.2 源根之外的java文件1.3 idea取消所有断点1.4 idea使用非模式提交界面1.5 用Service窗口展示所有服务及端口1.6 idea编码问题(加载配置文件失败)II idea 换行后自动缩进4个空格,怎么取消?I 常见问题 1.1 取消maven忽略文件…...

Spring AOP 切面按照一定规则切片并行查询Mapper并返回

需求: 有时候我们在查询mapper层时,有时候可能由于入参数据过大或者查询的范围较大,导致查询性能较慢,此时 我们需要将原本的查询按照一定规则将查询范围进行切面,然后分片查询,最后将查询结果进行组装合并…...

【vue3|第4期】Vue3的选项式与组合式

日期:2024年5月30日 作者:Commas 签名:(ง •_•)ง 积跬步以致千里,积小流以成江海…… 注释:如果您觉得有所帮助,帮忙点个赞,也可以关注我,我们一起成长;如果有不对的地方…...

算法训练营第四十五天 | LeetCode 1049 最后一块石头的重量II、LeetCode 494 目标和、LeetCode 474 一和零

LeetCode 1049 最后一块石头的重量 继续昨天没有详细说的01背包问题往下继续说。01背包问题是将dp从一维问题升维到二维之后会遇到的一类典型问题。dp数组自然而然地是一个横坐标表示物品序号-1,纵坐标表示背包重量的二维数组。01背包由一个背包是否放该物品并比照后…...

【数据结构与算法(C 语言)】栈的基本操作函数(动图演示) 及 栈的实际应用之一:进制转换

目录 1. 前言2. 结构及基本操作函数:2.1 栈的结构类型 Stack2.2 初始化栈 InitStack2.3 销毁栈 DestroyStack2.4 清空栈 ClearStack2.5 判断栈是否为空 StackEmpty2.6 获取stack的长度 StackLength2.7 获取栈顶元素 GetTop2.8 入栈 Push2.9 出栈 Pop2.10 访问元素2.…...

[原创]C++ 11的thread_local线程局部变量与Lambda表达式配合使用, 却引发致命的, 难以发现的冲突.

[简介] 常用网名: 猪头三 出生日期: 1981.XX.XX QQ联系: 643439947 个人网站: 80x86汇编小站 https://www.x86asm.org 编程生涯: 2001年~至今[共22年] 职业生涯: 20年 开发语言: C/C、80x86ASM、PHP、Perl、Objective-C、Object Pascal、C#、Python 开发工具: Visual Studio、D…...

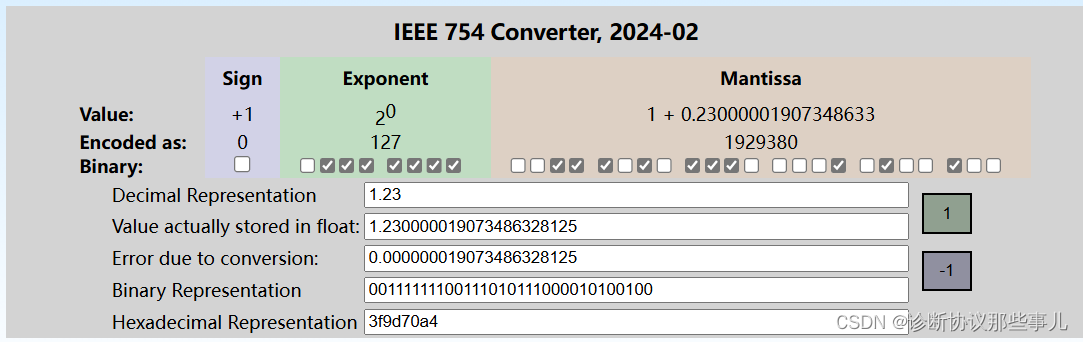

C语言-单精度和双精度浮点型

文章目录 一、遇到的问题二、解决方案三、问题根因float和double的区别: 总结-浮点数 一、遇到的问题 将NXP项目的代码移植到RH850F1K的项目上时,程序运行异常: u16Volt (uint16)((double)u16ADVal * (double)6.3) 执行到这一行程序就跑飞了…...

STM32学习问题总结(2)—CubeMX生成项目后串口没效果和Microlib

检查完所有的硬件和软件部分,最后发现,又是Keil的设置问题,啊啊啊啊 打开Keil的魔术棒,勾选Target的Use Microlib选项即可,但这并不是最佳方案 最终解决方案: 参考:http://t.csdnimg.cn/2Tjfc…...

【数据结构与算法 | 二叉树篇】二叉树的前中后序遍历(递归版本)

1. 二叉树的概念 (1). 二叉树的结构 借用了一下力扣的模板 public class TreeNode {int val;TreeNode left;TreeNode right;TreeNode() {}TreeNode(int val) { this.val val; }TreeNode(int val, TreeNode left, TreeNode right) {this.val val;this.left left;this.righ…...

Python exp用法:深入探索指数函数的奥秘

Python exp用法:深入探索指数函数的奥秘 在Python中,exp是一个非常重要的数学函数,它属于math模块的一部分,用于计算自然数e的指数。自然数e是一个无理数,约等于2.71828,它在数学、物理和工程等领域有着广…...

《利红AI企业级应用新标准等级体系》正式发布

各相关单位及合作伙伴: 为助力企业推动人工智能技术在实体经济中的科学落地,经公司研究决定,现正式发布《利红AI企业级应用新标准等级体系》(以下简称"本标准")。现将有关事项公告如下: 一、新…...

Deepoc 具身智能开发板,解锁更安全高效清扫新体验

在家庭客厅、书房,或是小型商铺、办公室等场景里,地面杂物、低矮家具、墙角缝隙随处可见,布局复杂又不规则。带机械臂的清扫机器人,早已成为不少人解放双手的好帮手,但传统设备在实际使用中,总难避开一些痛…...

)

Linux 系统编程 文件篇 (二)

[TOC] Linux 系统编程 文件篇 (二) 1 open 函数介绍 1.1 标记位 上一篇的结尾,我们讲到了我们用的打开文件的库函数其实是封装了,这个 open 的系统调用,然后解释了这个 open 函数的 这个标记位,flags 是一个…...

西南交通大学【数电实验之Modelsim仿真全流程实战】

1. 从零开始搭建Modelsim仿真环境 第一次接触数字电路仿真的同学可能会觉得Modelsim界面复杂,其实只要跟着步骤一步步操作,半小时就能跑通第一个仿真案例。我当年在西南交大做数电实验时,也经历过从一脸懵到熟练操作的过程,这里把…...

)

别再只盯着原理图了!FPGA/SoC硬件工程师必看的RGMII接口PCB布线实战指南(含时序约束与等长规则)

RGMII接口PCB设计实战:从时序规范到千兆以太网稳定通信 在FPGA和SoC硬件开发中,RGMII接口设计一直是工程师们又爱又恨的挑战。爱它的简洁高效——相比GMII接口减少了近一半的引脚数量;恨它的时序敏感——一个看似微小的PCB布线失误就可能导致…...

的实战选型指南)

别再纠结选哪种了!一文讲透无人机测深三剑客(激光雷达/测深仪/GPR)的实战选型指南

无人机测深技术三剑客:激光雷达、测深仪与探地雷达的深度选型指南 当无人机遇上水深测量,技术选型往往成为项目成败的关键。在河道整治、水库清淤、海岸线测绘等场景中,工程师们常面临一个核心难题:如何在激光雷达、测深仪和探地雷…...

tRPC全栈类型安全实战

tRPC全栈类型安全实战:告别API类型地狱,TypeScript前后端零成本类型共享 摘要:在全栈TypeScript项目中,前后端类型不同步是最常见的Bug来源之一。tRPC通过编译时类型推导,实现了端到端的类型安全——前端调用后端API就像调用本地函数一样,类型自动推导、错误提前暴露。本…...

高速串行接口CDR锁定判断:从原理到实战的验证方法论

1. 项目概述:理解CDR锁定的核心价值在数字电路设计,特别是高速串行接口(如PCIe、USB、SATA、DDR)和时钟数据恢复(CDR)电路验证中,“CDR成功锁定”是一个决定系统能否正常工作的“生命线”信号。…...

【懒人专用】Windows 端 Open Claw v 2.7.5 全自动部署图文教程

📌 前言 2026 年开源圈热门的「数字员工」OpenClaw(昵称小龙虾),GitHub 星标突破 28 万,凭借本地运行 零代码操作 自动干活的核心优势广受关注!很多人误以为它是普通聊天 AI,实则是能真正操控…...

如何在Windows电脑上直接运行安卓应用:APK安装器终极解决方案

如何在Windows电脑上直接运行安卓应用:APK安装器终极解决方案 【免费下载链接】APK-Installer An Android Application Installer for Windows 项目地址: https://gitcode.com/GitHub_Trending/ap/APK-Installer 你是否曾经希望在Windows电脑上直接运行安卓应…...