Mini2440 start.s 修改支持串口输出,方便调试 (四)

经常会遇到点板子的时候,板子没有任何反应!怎么知道板子有没有在正常启动,在uboot阶段 start.s 中加入串口打印信息是很有必要的!

输出串口信息

***UART:mini-2440-uBoot***

***UART:mini-2440-uBoot***

***UART:mini-2440-uBoot******UART:mini-2440-uBoot***#include <config.h>

#include <version.h>

#if defined(CONFIG_S3C2410)

#include <s3c2410.h>

#elif defined(CONFIG_S3C2440) || defined(CONFIG_S3C2442)

#include <s3c2440.h>

#elif defined(CONFIG_S3C2443)

#include <s3c2443.h>

#endif

#include <status_led.h>/**************************************************************************** Jump vector table as in table 3.1 in [1]***************************************************************************/.globl _start

_start: b start_codeldr pc, _undefined_instructionldr pc, _software_interruptldr pc, _prefetch_abortldr pc, _data_abortldr pc, _not_usedldr pc, _irqldr pc, _fiq_undefined_instruction: .word undefined_instruction

_software_interrupt: .word software_interrupt

_prefetch_abort: .word prefetch_abort

_data_abort: .word data_abort

_not_used: .word not_used

_irq: .word irq

_fiq: .word fiq.balignl 16,0xdeadbeef/**************************************************************************** Startup Code (called from the ARM reset exception vector)** do important init only if we don t start from memory!* relocate armboot to ram* setup stack* jump to second stage***************************************************************************//* Must follow the .balign above, so we get a well-known address ! */

#ifdef CFG_PREBOOT_OVERRIDE

.globl preboot_override

preboot_override:.word 0

#endif/* Must follow preboot_override , so we get a well-known address ! */

#ifdef CFG_ENV_OVERRIDE

.globl env_override

env_override:.word 0

#endif#ifdef CONFIG_S3C2410_NAND_BOOT

.globl booted_from_nand

booted_from_nand:.word 0

_booted_from_nand:.word booted_from_nand

#endif /* CONFIG_S3C2410_NAND_BOOT */#ifndef CFG_NO_FLASH

.globl booted_from_nor

booted_from_nor:.word 0

_booted_from_nor:.word booted_from_nor

_end_if_0:.word __bss_start-_start

#endif /* !CFG_NO_FLASH */_TEXT_BASE:.word TEXT_BASE.globl _armboot_start

_armboot_start:.word _start/** These are defined in the board-specific linker script.*/

.globl _bss_start

_bss_start:.word __bss_start.globl _bss_end

_bss_end:.word _end#ifdef CONFIG_USE_IRQ

/* IRQ stack memory (calculated at run-time) */

.globl IRQ_STACK_START

IRQ_STACK_START:.word 0x0badc0de/* IRQ stack memory (calculated at run-time) */

.globl FIQ_STACK_START

FIQ_STACK_START:.word 0x0badc0de

#endif/** the actual start code*/start_code:/** set the cpu to SVC32 mode*/mrs r0,cpsrbic r0,r0,#0x1forr r0,r0,#0xd3msr cpsr,r0/* in case we run from the s3c24xx NAND stepping stone, the symbols* for LED support are in lib_arm/board.o, i.e. outside of the* steppingstone */

#ifndef CONFIG_S3C2410_NAND_BOOTbl coloured_LED_initbl red_LED_on

#endif#if defined(CONFIG_AT91RM9200DK) || defined(CONFIG_AT91RM9200EK) || defined(CONFIG_AT91RM9200DF)/** relocate exception table*/ldr r0, =_startldr r1, =0x0mov r2, #16

copyex:subs r2, r2, #1ldr r3, [r0], #4str r3, [r1], #4bne copyex

#endif#if defined(CONFIG_S3C2400) || defined(CONFIG_S3C2410) || defined(CONFIG_S3C2440) || \defined(CONFIG_S3C2442) || defined(CONFIG_S3C2443)/* turn off the watchdog */# if defined(CONFIG_S3C2400)

# define pWTCON 0x15300000

# define INTMSK 0x14400008 /* Interupt-Controller base addresses */

# define CLKDIVN 0x14800014 /* clock divisor register */

#elif defined(CONFIG_S3C2410) || defined(CONFIG_S3C2440) || defined(CONFIG_S3C2442)

# define pWTCON 0x53000000

# define INTMSK 0x4A000008 /* Interupt-Controller base addresses */

# define INTSUBMSK 0x4A00001C

# define CLKDIVN 0x4C000014 /* clock divisor register */

# endif#if defined(CONFIG_S3C2410)

# define INTSUBMSK_val 0x7ff

# define MPLLCON_val ((0x90 << 12) + (0x7 << 4) + 0x0) /* 202 MHz */

# define UPLLCON_val ((0x78 << 12) + (0x2 << 4) + 0x3)

# define CLKDIVN_val 3 /* FCLK:HCLK:PCLK = 1:2:4 */

#elif defined(CONFIG_S3C2440)

# define INTSUBMSK_val 0xffff

#if (CONFIG_SYS_CLK_FREQ == 16934400)

# define MPLLCON_val ((0x61 << 12) + (0x1 << 4) + 0x2) /* 296.35 MHz */

# define UPLLCON_val ((0x3c << 12) + (0x4 << 4) + 0x2) /* 47.98 MHz */

#elif (CONFIG_SYS_CLK_FREQ == 12000000)

# define MPLLCON_val ((0x44 << 12) + (0x1 << 4) + 0x1) /* 304.00 MHz */

# define UPLLCON_val ((0x38 << 12) + (0x2 << 4) + 0x2) /* 48.00 MHz */

#endif

# define CLKDIVN_val 7 /* FCLK:HCLK:PCLK = 1:3:6 */

# define CAMDIVN 0x4C000018

#elif defined(CONFIG_S3C2442)

# define INTSUBMSK_val 0xffff

# if (CONFIG_SYS_CLK_FREQ == 12000000)

# define MPLLCON_val ((142 << 12) + (7 << 4) + 1)

# define UPLLCON_val (( 88 << 12) + (4 << 4) + 2)

# elif (CONFIG_SYS_CLK_FREQ == 16934400)

# define MPLLCON_val ((181 << 12) + (14<< 4) + 1)

# define UPLLCON_val (( 26 << 12) + (4 << 4) + 1)

# endif

# define CLKDIVN_val 7 /* FCLK:HCLK:PCLK = 1:3:6 */

# define CAMDIVN 0x4C000018

#elif defined(CONFIG_S3C2443)

# define INTSUBMSK_val 0x1fffffff

# define EPLLCON_val ((40 << 16) | (1 << 8) | (1)) /* 96 MHz */

# define MPLLCON_val ((81 << 16) | (2 << 8) | (0)) /* 1068 MHz */

# define CLKDIV0_val ((8 << 9) | (1 << 4) | (1 << 3) | (1 << 2)

#endifldr r0, =pWTCONmov r1, #0x0str r1, [r0]/** mask all IRQs by setting all bits in the INTMR - default*/mov r1, #0xffffffffldr r0, =INTMSKstr r1, [r0]

# if defined(CONFIG_S3C2410) || defined(CONFIG_S3C2440) || defined(CONFIG_S3C2442) || \defined(CONFIG_S3C2443)ldr r1, =INTSUBMSK_valldr r0, =INTSUBMSKstr r1, [r0]

# endif#if defined(CONFIG_S3C2440) || defined(CONFIG_S3C2442)/* Make sure we get FCLK:HCLK:PCLK */ldr r0, =CAMDIVNmov r1, #0str r1, [r0]

#endif/* Clock asynchronous mode */mrc p15, 0, r1, c1, c0, 0orr r1, r1, #0xc0000000mcr p15, 0, r1, c1, c0, 0#if defined(CONFIG_S3C2443)

#define LOCKCON0 0x4c000000

#define LOCKCON1 0x4c000004

#define MPLLCON 0x4c000010

#define EPLLCON 0x4c000018ldr r0, =CLKDIV0ldr r1, =CLKDIV0_valstr r1, [r0]/* set safe (way too long) locktime for both PLLs */ldr r0, =LOCKCON0mov r1, #0xffffffstr r1, [r0]ldr r0, =LOCKCON1str r1, [r0]/* configure MPLL */ldr r0, =MPLLCONldr r1, =MPLLCON_valstr r1, [r0]/* select MPLL clock out for SYSCLK */ldr r0, =CLKSRCldr r1, [r0]orr r1, r1, #0x10str r1, [r0]#if 0/* configure EPLL */ldr r0, =EPLLCONldr r1, =EPLLCON_valstr r1, [r0]

#endif#else /* i.e. 2440, 2410 and 2440 */#ifndef CONFIG_MINI2440 /* cpu_init_crit is called right afterward */

#define LOCKTIME 0x4c000000

#define UPLLCON 0x4c000008ldr r0, =LOCKTIMEmov r1, #0xffffffstr r1, [r0]ldr r0, =UPLLCONldr r1, =UPLLCON_valstr r1, [r0]/* Page 7-19, seven nops between UPLL and MPLL */nopnopnopnopnopnopnopldr r1, =MPLLCON_valstr r1, [r0, #-4] /* MPLLCON *//* FCLK:HCLK:PCLK */ldr r0, =CLKDIVNmov r1, #CLKDIVN_valstr r1, [r0]

#endif#if 1/* enable uart */ldr r0, =0x4c00000c /* clkcon */ldr r1, =0x7fff0 /* all clocks on */str r1, [r0]/* gpio UART0 init */ldr r0, =0x56000070mov r1, #0xaastr r1, [r0]/* init uart */ldr r0, =0x50000000mov r1, #0x03str r1, [r0]ldr r1, =0x245str r1, [r0, #0x04]mov r1, #0x01str r1, [r0, #0x08]mov r1, #0x00str r1, [r0, #0x0c]mov r1, #0x1astr r1, [r0, #0x28]bl usart0_initbl usart0_send//ldr r0,=0x1230//bl usart0_print_r10//b . //程序停在在这里(死循环)#endif#endif /* ! CONFIG_MINI2440 */#endif /* CONFIG_S3C2400 || CONFIG_S3C2410 || CONFIG_S3C2440 || CONFIG_S3C2442CONFIG_S3C2443 */#ifndef CONFIG_SKIP_LOWLEVEL_INIT

#ifndef CONFIG_LL_INIT_NAND_ONLYbl cpu_init_crit //-------------> go

#endif#if defined(CONFIG_AT91RM9200) || defined(CONFIG_S3C2410) || \defined(CONFIG_S3C2440) || defined(CONFIG_S3C2442) || \defined(CONFIG_S3C2443)#ifndef CONFIG_SKIP_RELOCATE_UBOOTadr r0, _start /* r0 <- current position of code */#ifdef CONFIG_S3C2410_NAND_BOOT/* are we running from NAND ? */

#define BWSCON 0x48000000ldr r1, =BWSCON /* Z = CPU booted from NAND */ldr r1, [r1]tst r1, #6 /* BWSCON[2:1] = OM[1:0] */teqeq r0, #0 /* Z &= running at address 0 */beq nand_load //-------------> go

#endif /* CONFIG_S3C2410_NAND_BOOT */

/*No.2 '***UART:mini-2440-uBoot***' */bl usart0_initbl usart0_send

relocate: /* relocate U-Boot to RAM */teq r0, #0 /* running at address 0 ? */bleq may_resume /* yes -> do low-level setup */adr r0, _start /* the above may have clobbered r0 */ldr r1, _TEXT_BASE /* test if we run from flash or RAM */cmp r0, r1 /* don t reloc during debug */beq done_relocateldr r2, _armboot_startldr r3, _bss_startsub r2, r3, r2 /* r2 <- size of armboot */add r2, r0, r2 /* r2 <- source end address */copy_loop:ldmia r0!, {r3-r10} /* copy from source address [r0] */stmia r1!, {r3-r10} /* copy to target address [r1] */cmp r0, r2 /* until source end address [r2] */ble copy_loop#ifndef CFG_NO_FLASHldr r0, _end_if_0 /* are we booting from NOR ? */cmp r0, r2ldreq r0, _booted_from_nor /* remember that we ve booted from */moveq r1, #1 /* NOR */streqb r1, [r0]

#endif /* !CFG_NO_FLASH */mov r0, #0 /* flush v3/v4 cache */mcr p15, 0, r0, c7, c7, 0ldr pc, _done_relocate /* jump to relocated code */

_done_relocate:.word done_relocate#ifdef CONFIG_S3C2410_NAND_BOOT

nand_load:bl usart0_initbl usart0_sendbl may_resume /* low-level setup and resume */@ reset NAND

#if defined(CONFIG_S3C2410)mov r1, #S3C2410_NAND_BASEldr r2, =0xf842 @ initial value enable tacls=3,rph0=6,rph1=0str r2, [r1, #oNFCONF]ldr r2, [r1, #oNFCONF]bic r2, r2, #0x800 @ enable chipstr r2, [r1, #oNFCONF]mov r2, #0xff @ RESET commandstrb r2, [r1, #oNFCMD]mov r3, #0 @ wait

1: add r3, r3, #0x1cmp r3, #0xablt 1b

2: ldr r2, [r1, #oNFSTAT] @ wait readytst r2, #0x1beq 2bldr r2, [r1, #oNFCONF]orr r2, r2, #0x800 @ disable chipstr r2, [r1, #oNFCONF]

#elif defined(CONFIG_S3C2440) || defined(CONFIG_S3C2442)mov r1, #S3C2440_NAND_BASEldr r2, =0xfff0 @ initial value tacls=3,rph0=7,rph1=7ldr r3, [r1, #oNFCONF]orr r3, r3, r2str r3, [r1, #oNFCONF]ldr r3, [r1, #oNFCONT]orr r3, r3, #1 @ enable nand controllerstr r3, [r1, #oNFCONT]

#endif /* CONFIG_S3C2440 || CONFIG_S3C2442 */ldr r0, _TEXT_BASE /* upper 128 KiB: relocated uboot */sub r0, r0, #CFG_MALLOC_LEN /* malloc area */sub r0, r0, #CFG_GBL_DATA_SIZE /* bdinfo */

#ifdef CONFIG_USE_IRQsub r0, r0, #(CONFIG_STACKSIZE_IRQ+CONFIG_STACKSIZE_FIQ)

#endifsub sp, r0, #12 /* leave 3 words for abort-stack */@ copy u-boot to RAMldr r0, _TEXT_BASEmov r1, #0x0mov r2, #CFG_UBOOT_SIZEbl nand_read_lltst r0, #0x0beq ok_nand_read

#ifdef CONFIG_DEBUG_LL

bad_nand_read:ldr r0, STR_FAILldr r1, SerBasebl PrintWord

1: b 1b @ infinite loop

#endifok_nand_read:

#ifdef CONFIG_DEBUG_LLldr r0, STR_OKldr r1, SerBasebl PrintWord

#endif@ verifymov r0, #0@ldr r1, =0x33f00000ldr r1, _TEXT_BASEmov r2, #0x400 @ 4 bytes * 1024 = 4K-bytes

go_next:ldr r3, [r0], #4ldr r4, [r1], #4teq r3, r4bne notmatchsubs r2, r2, #4beq done_nand_readbne go_next

notmatch:

#ifdef CONFIG_DEBUG_LLsub r0, r0, #4ldr r1, SerBasebl PrintHexWordldr r0, STR_FAILldr r1, SerBasebl PrintWord

#endif

1: b 1b

done_nand_read:ldr r0, _booted_from_nandmov r1, #1strb r1, [r0]

#endif /* CONFIG_S3C2410_NAND_BOOT */

done_relocate:#if defined(CONFIG_USE_IRQ) && (defined(CONFIG_S3C2410) || \defined(CONFIG_S3C2440) || defined(CONFIG_S3C2442))/* In the case of the S3C2410, if we ve somehow magically (JTAG, ...)ended up in RAM, then that ram is mapped to 0x30000000 and not 0.So we need to copy the interrupt vectors, etc. */mov r0, #0ldr r1, _TEXT_BASEmov r2, #0x40

irqvec_cpy_next:ldr r3, [r1], #4str r3, [r0], #4subs r2, r2, #4bne irqvec_cpy_next

#endif /* CONFIG_USE_IRQ */#endif /* CONFIG_SKIP_RELOCATE_UBOOT */

#endif/* Set up the stack */

stack_setup:ldr r0, _TEXT_BASE /* upper 128 KiB: relocated uboot */sub r0, r0, #CFG_MALLOC_LEN /* malloc area */sub r0, r0, #CFG_GBL_DATA_SIZE /* bdinfo */

#ifdef CONFIG_USE_IRQsub r0, r0, #(CONFIG_STACKSIZE_IRQ+CONFIG_STACKSIZE_FIQ)

#endifsub sp, r0, #12 /* leave 3 words for abort-stack */clear_bss:ldr r0, _bss_start /* find start of bss segment */ldr r1, _bss_end /* stop here */mov r2, #0x00000000 /* clear */clbss_l:str r2, [r0] /* clear loop... */add r0, r0, #4cmp r0, r1ble clbss_lldr pc, _start_armboot

/*go to uboot*/

_start_armboot: .word start_armboot/**************************************************************************** CPU_init_critical registers** setup important registers* setup memory timing***************************************************************************/#ifndef CONFIG_SKIP_LOWLEVEL_INIT

cpu_init_crit:/** flush v4 I/D caches*/mov r0, #0mcr p15, 0, r0, c7, c7, 0 /* flush v3/v4 cache */mcr p15, 0, r0, c8, c7, 0 /* flush v4 TLB *//** disable MMU stuff and caches*/mrc p15, 0, r0, c1, c0, 0bic r0, r0, #0x00002300 @ clear bits 13, 9:8 (--V- --RS)bic r0, r0, #0x00000087 @ clear bits 7, 2:0 (B--- -CAM)orr r0, r0, #0x00000002 @ set bit 2 (A) Alignorr r0, r0, #0x00001000 @ set bit 12 (I) I-Cachemcr p15, 0, r0, c1, c0, 0/** before relocating, we have to setup RAM timing* because memory timing is board-dependend, you will* find a lowlevel_init.S in your board directory.*/mov ip, lr

#if defined(CONFIG_AT91RM9200DK) || defined(CONFIG_AT91RM9200EK) || defined(CONFIG_AT91RM9200DF)#elsebl lowlevel_init

#endifmov lr, ipmov pc, lr

#endif /* CONFIG_SKIP_LOWLEVEL_INIT *//**************************************************************************** may_resume** Bring up memory and check if we re coming out of suspend.***************************************************************************/may_resume:mov r10, lr /* we may call cpu_init_crit *//* take sdram out of power down */ldr r0, =0x56000080 /* misccr */ldr r1, [ r0 ]bic r1, r1, #(S3C2410_MISCCR_nEN_SCLK0 | S3C2410_MISCCR_nEN_SCLK1 | S3C2410_MISCCR_nEN_SCLKE)str r1, [ r0 ]/* ensure signals stabalise */mov r1, #128

1: subs r1, r1, #1bpl 1b#if !defined(CONFIG_SKIP_LOWLEVEL_INIT) && defined(CONFIG_LL_INIT_NAND_ONLY)bl cpu_init_crit

#endif

#if defined(CONFIG_S3C2410) || defined(CONFIG_S3C2440) || defined(CONFIG_S3C2442)/* ensure some refresh has happened */ldr r1, =0xfffff

1: subs r1, r1, #1bpl 1b/* capture full EINT situation into gstatus 4 */ldr r0, =0x4A000000 /* SRCPND */ldr r1, [ r0 ]and r1, r1, #0xfldr r0, =0x560000BC /* gstatus4 */str r1, [ r0 ]ldr r0, =0x560000A8 /* EINTPEND */ldr r1, [ r0 ]ldr r0, =0xfff0and r1, r1, r0ldr r0, =0x560000BC /* gstatus4 */ldr r0, [ r0 ]orr r1, r1, r0ldr r0, =0x560000BC /* gstatus4 */str r1, [ r0 ]/* test for resume */ldr r1, =0x560000B4 /* gstatus2 */ldr r0, [ r1 ]tst r0, #0x02 /* is this resume from power down *//* well, if it was, we are going to jump to* whatever address we stashed in gstatus3,* and gstatus4 will hold the wake interrupt* source for the OS to look at*/ldrne pc, [r1, #4]

#endif /* CONFIG_S3C2410 || CONFIG_S3C244 || CONFIG_S3C2442 */

#endif /* CONFIG_SKIP_LOWLEVEL_INIT */mov pc, r10/**************************************************************************** Interrupt handling***************************************************************************/@

@ IRQ stack frame.

@

#define S_FRAME_SIZE 72#define S_OLD_R0 68

#define S_PSR 64

#define S_PC 60

#define S_LR 56

#define S_SP 52#define S_IP 48

#define S_FP 44

#define S_R10 40

#define S_R9 36

#define S_R8 32

#define S_R7 28

#define S_R6 24

#define S_R5 20

#define S_R4 16

#define S_R3 12

#define S_R2 8

#define S_R1 4

#define S_R0 0#define MODE_SVC 0x13

#define I_BIT 0x80/** use bad_save_user_regs for abort/prefetch/undef/swi ...* use irq_save_user_regs / irq_restore_user_regs for IRQ/FIQ handling*/.macro bad_save_user_regssub sp, sp, #S_FRAME_SIZEstmia sp, {r0 - r12} @ Calling r0-r12ldr r2, _armboot_startsub r2, r2, #(CONFIG_STACKSIZE+CFG_MALLOC_LEN)sub r2, r2, #(CFG_GBL_DATA_SIZE+8) @ set base 2 words into abort stackldmia r2, {r2 - r3} @ get pc, cpsradd r0, sp, #S_FRAME_SIZE @ restore sp_SVCadd r5, sp, #S_SPmov r1, lrstmia r5, {r0 - r3} @ save sp_SVC, lr_SVC, pc, cpsrmov r0, sp.endm.macro irq_save_user_regssub sp, sp, #S_FRAME_SIZEstmia sp, {r0 - r12} @ Calling r0-r12add r7, sp, #S_PCstmdb r7, {sp, lr}^ @ Calling SP, LRstr lr, [r7, #0] @ Save calling PCmrs r6, spsrstr r6, [r7, #4] @ Save CPSRstr r0, [r7, #8] @ Save OLD_R0mov r0, sp.endm.macro irq_restore_user_regsldmia sp, {r0 - lr}^ @ Calling r0 - lrmov r0, r0ldr lr, [sp, #S_PC] @ Get PCadd sp, sp, #S_FRAME_SIZEsubs pc, lr, #4 @ return & move spsr_svc into cpsr.endm.macro get_bad_stackldr r13, _armboot_start @ setup our mode stacksub r13, r13, #(CONFIG_STACKSIZE+CFG_MALLOC_LEN)sub r13, r13, #(CFG_GBL_DATA_SIZE+8) @ reserved a couple spots in abort stackstr lr, [r13] @ save caller lr / spsrmrs lr, spsrstr lr, [r13, #4]mov r13, #MODE_SVC @ prepare SVC-Mode@ msr spsr_c, r13msr spsr, r13mov lr, pcmovs pc, lr.endm.macro get_irq_stack @ setup IRQ stackldr sp, IRQ_STACK_START.endm.macro get_fiq_stack @ setup FIQ stackldr sp, FIQ_STACK_START.endm/** exception handlers*/.align 5

undefined_instruction:get_bad_stackbad_save_user_regsbl do_undefined_instruction.align 5

software_interrupt:get_bad_stackbad_save_user_regsbl do_software_interrupt.align 5

prefetch_abort:get_bad_stackbad_save_user_regsbl do_prefetch_abort.align 5

data_abort:get_bad_stackbad_save_user_regsbl do_data_abort.align 5

not_used:get_bad_stackbad_save_user_regsbl do_not_used#ifdef CONFIG_USE_IRQ.align 5

irq:get_irq_stackirq_save_user_regsbl do_irqirq_restore_user_regs.align 5

fiq:get_fiq_stack/* someone ought to write a more effiction fiq_save_user_regs */irq_save_user_regsbl do_fiqirq_restore_user_regs#else.align 5

irq:get_bad_stackbad_save_user_regsbl do_irq.align 5

fiq:get_bad_stackbad_save_user_regsbl do_fiq#endif/** armboot - Startup Code for ARM920 CPU-core** Copyright (c) 2001 Marius Gr鰃er <mag@sysgo.de>* Copyright (c) 2002 Alex Z黳ke <azu@sysgo.de>* Copyright (c) 2002 Gary Jennejohn <gj@denx.de>** S3C2410 NAND portions* Copyright (c) 2001 MIZI Research, Inc.* Copyright (c) 2006 OpenMoko, Inc. (Harald Welte <laforge@openmmoko.org>** See file CREDITS for list of people who contributed to this* project.** This program is free software; you can redistribute it and/or* modify it under the terms of the GNU General Public License as* published by the Free Software Foundation; either version 2 of* the License, or (at your option) any later version.** This program is distributed in the hope that it will be useful,* but WITHOUT ANY WARRANTY; without even the implied warranty of* MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the* GNU General Public License for more details.** You should have received a copy of the GNU General Public License* along with this program; if not, write to the Free Software* Foundation, Inc., 59 Temple Place, Suite 330, Boston,* MA 02111-1307 USA*/#include <config.h>

#include <version.h>

#if defined(CONFIG_S3C2410)

#include <s3c2410.h>

#elif defined(CONFIG_S3C2440) || defined(CONFIG_S3C2442)

#include <s3c2440.h>

#elif defined(CONFIG_S3C2443)

#include <s3c2443.h>

#endif

#include <status_led.h>/**************************************************************************** Jump vector table as in table 3.1 in [1]***************************************************************************/.globl _start

_start: b start_codeldr pc, _undefined_instructionldr pc, _software_interruptldr pc, _prefetch_abortldr pc, _data_abortldr pc, _not_usedldr pc, _irqldr pc, _fiq_undefined_instruction: .word undefined_instruction

_software_interrupt: .word software_interrupt

_prefetch_abort: .word prefetch_abort

_data_abort: .word data_abort

_not_used: .word not_used

_irq: .word irq

_fiq: .word fiq.balignl 16,0xdeadbeef/**************************************************************************** Startup Code (called from the ARM reset exception vector)** do important init only if we don t start from memory!* relocate armboot to ram* setup stack* jump to second stage***************************************************************************//* Must follow the .balign above, so we get a well-known address ! */

#ifdef CFG_PREBOOT_OVERRIDE

.globl preboot_override

preboot_override:.word 0

#endif/* Must follow preboot_override , so we get a well-known address ! */

#ifdef CFG_ENV_OVERRIDE

.globl env_override

env_override:.word 0

#endif#ifdef CONFIG_S3C2410_NAND_BOOT

.globl booted_from_nand

booted_from_nand:.word 0

_booted_from_nand:.word booted_from_nand

#endif /* CONFIG_S3C2410_NAND_BOOT */#ifndef CFG_NO_FLASH

.globl booted_from_nor

booted_from_nor:.word 0

_booted_from_nor:.word booted_from_nor

_end_if_0:.word __bss_start-_start

#endif /* !CFG_NO_FLASH */_TEXT_BASE:.word TEXT_BASE.globl _armboot_start

_armboot_start:.word _start/** These are defined in the board-specific linker script.*/

.globl _bss_start

_bss_start:.word __bss_start.globl _bss_end

_bss_end:.word _end#ifdef CONFIG_USE_IRQ

/* IRQ stack memory (calculated at run-time) */

.globl IRQ_STACK_START

IRQ_STACK_START:.word 0x0badc0de/* IRQ stack memory (calculated at run-time) */

.globl FIQ_STACK_START

FIQ_STACK_START:.word 0x0badc0de

#endif/** the actual start code*/start_code:/** set the cpu to SVC32 mode*/mrs r0,cpsrbic r0,r0,#0x1forr r0,r0,#0xd3msr cpsr,r0/* in case we run from the s3c24xx NAND stepping stone, the symbols* for LED support are in lib_arm/board.o, i.e. outside of the* steppingstone */

#ifndef CONFIG_S3C2410_NAND_BOOTbl coloured_LED_initbl red_LED_on

#endif#if defined(CONFIG_AT91RM9200DK) || defined(CONFIG_AT91RM9200EK) || defined(CONFIG_AT91RM9200DF)/** relocate exception table*/ldr r0, =_startldr r1, =0x0mov r2, #16

copyex:subs r2, r2, #1ldr r3, [r0], #4str r3, [r1], #4bne copyex

#endif#if defined(CONFIG_S3C2400) || defined(CONFIG_S3C2410) || defined(CONFIG_S3C2440) || \defined(CONFIG_S3C2442) || defined(CONFIG_S3C2443)/* turn off the watchdog */# if defined(CONFIG_S3C2400)

# define pWTCON 0x15300000

# define INTMSK 0x14400008 /* Interupt-Controller base addresses */

# define CLKDIVN 0x14800014 /* clock divisor register */

#elif defined(CONFIG_S3C2410) || defined(CONFIG_S3C2440) || defined(CONFIG_S3C2442)

# define pWTCON 0x53000000

# define INTMSK 0x4A000008 /* Interupt-Controller base addresses */

# define INTSUBMSK 0x4A00001C

# define CLKDIVN 0x4C000014 /* clock divisor register */

# endif#if defined(CONFIG_S3C2410)

# define INTSUBMSK_val 0x7ff

# define MPLLCON_val ((0x90 << 12) + (0x7 << 4) + 0x0) /* 202 MHz */

# define UPLLCON_val ((0x78 << 12) + (0x2 << 4) + 0x3)

# define CLKDIVN_val 3 /* FCLK:HCLK:PCLK = 1:2:4 */

#elif defined(CONFIG_S3C2440)

# define INTSUBMSK_val 0xffff

#if (CONFIG_SYS_CLK_FREQ == 16934400)

# define MPLLCON_val ((0x61 << 12) + (0x1 << 4) + 0x2) /* 296.35 MHz */

# define UPLLCON_val ((0x3c << 12) + (0x4 << 4) + 0x2) /* 47.98 MHz */

#elif (CONFIG_SYS_CLK_FREQ == 12000000)

# define MPLLCON_val ((0x44 << 12) + (0x1 << 4) + 0x1) /* 304.00 MHz */

# define UPLLCON_val ((0x38 << 12) + (0x2 << 4) + 0x2) /* 48.00 MHz */

#endif

# define CLKDIVN_val 7 /* FCLK:HCLK:PCLK = 1:3:6 */

# define CAMDIVN 0x4C000018

#elif defined(CONFIG_S3C2442)

# define INTSUBMSK_val 0xffff

# if (CONFIG_SYS_CLK_FREQ == 12000000)

# define MPLLCON_val ((142 << 12) + (7 << 4) + 1)

# define UPLLCON_val (( 88 << 12) + (4 << 4) + 2)

# elif (CONFIG_SYS_CLK_FREQ == 16934400)

# define MPLLCON_val ((181 << 12) + (14<< 4) + 1)

# define UPLLCON_val (( 26 << 12) + (4 << 4) + 1)

# endif

# define CLKDIVN_val 7 /* FCLK:HCLK:PCLK = 1:3:6 */

# define CAMDIVN 0x4C000018

#elif defined(CONFIG_S3C2443)

# define INTSUBMSK_val 0x1fffffff

# define EPLLCON_val ((40 << 16) | (1 << 8) | (1)) /* 96 MHz */

# define MPLLCON_val ((81 << 16) | (2 << 8) | (0)) /* 1068 MHz */

# define CLKDIV0_val ((8 << 9) | (1 << 4) | (1 << 3) | (1 << 2)

#endifldr r0, =pWTCONmov r1, #0x0str r1, [r0]/** mask all IRQs by setting all bits in the INTMR - default*/mov r1, #0xffffffffldr r0, =INTMSKstr r1, [r0]

# if defined(CONFIG_S3C2410) || defined(CONFIG_S3C2440) || defined(CONFIG_S3C2442) || \defined(CONFIG_S3C2443)ldr r1, =INTSUBMSK_valldr r0, =INTSUBMSKstr r1, [r0]

# endif#if defined(CONFIG_S3C2440) || defined(CONFIG_S3C2442)/* Make sure we get FCLK:HCLK:PCLK */ldr r0, =CAMDIVNmov r1, #0str r1, [r0]

#endif/* Clock asynchronous mode */mrc p15, 0, r1, c1, c0, 0orr r1, r1, #0xc0000000mcr p15, 0, r1, c1, c0, 0#if defined(CONFIG_S3C2443)

#define LOCKCON0 0x4c000000

#define LOCKCON1 0x4c000004

#define MPLLCON 0x4c000010

#define EPLLCON 0x4c000018ldr r0, =CLKDIV0ldr r1, =CLKDIV0_valstr r1, [r0]/* set safe (way too long) locktime for both PLLs */ldr r0, =LOCKCON0mov r1, #0xffffffstr r1, [r0]ldr r0, =LOCKCON1str r1, [r0]/* configure MPLL */ldr r0, =MPLLCONldr r1, =MPLLCON_valstr r1, [r0]/* select MPLL clock out for SYSCLK */ldr r0, =CLKSRCldr r1, [r0]orr r1, r1, #0x10str r1, [r0]#if 0/* configure EPLL */ldr r0, =EPLLCONldr r1, =EPLLCON_valstr r1, [r0]

#endif#else /* i.e. 2440, 2410 and 2440 */#ifndef CONFIG_MINI2440 /* cpu_init_crit is called right afterward */

#define LOCKTIME 0x4c000000

#define UPLLCON 0x4c000008ldr r0, =LOCKTIMEmov r1, #0xffffffstr r1, [r0]ldr r0, =UPLLCONldr r1, =UPLLCON_valstr r1, [r0]/* Page 7-19, seven nops between UPLL and MPLL */nopnopnopnopnopnopnopldr r1, =MPLLCON_valstr r1, [r0, #-4] /* MPLLCON *//* FCLK:HCLK:PCLK */ldr r0, =CLKDIVNmov r1, #CLKDIVN_valstr r1, [r0]

#endif#if 1/* enable uart */ldr r0, =0x4c00000c /* clkcon */ldr r1, =0x7fff0 /* all clocks on */str r1, [r0]/* gpio UART0 init */ldr r0, =0x56000070mov r1, #0xaastr r1, [r0]/* init uart */ldr r0, =0x50000000mov r1, #0x03str r1, [r0]ldr r1, =0x245str r1, [r0, #0x04]mov r1, #0x01str r1, [r0, #0x08]mov r1, #0x00str r1, [r0, #0x0c]mov r1, #0x1astr r1, [r0, #0x28]bl usart0_initbl usart0_send//ldr r0,=0x1230//bl usart0_print_r10//b . //程序停在在这里(死循环)#endif#endif /* ! CONFIG_MINI2440 */#endif /* CONFIG_S3C2400 || CONFIG_S3C2410 || CONFIG_S3C2440 || CONFIG_S3C2442CONFIG_S3C2443 */#ifndef CONFIG_SKIP_LOWLEVEL_INIT

#ifndef CONFIG_LL_INIT_NAND_ONLYbl cpu_init_crit //-------------> go

#endif#if defined(CONFIG_AT91RM9200) || defined(CONFIG_S3C2410) || \defined(CONFIG_S3C2440) || defined(CONFIG_S3C2442) || \defined(CONFIG_S3C2443)#ifndef CONFIG_SKIP_RELOCATE_UBOOTadr r0, _start /* r0 <- current position of code */#ifdef CONFIG_S3C2410_NAND_BOOT/* are we running from NAND ? */

#define BWSCON 0x48000000ldr r1, =BWSCON /* Z = CPU booted from NAND */ldr r1, [r1]tst r1, #6 /* BWSCON[2:1] = OM[1:0] */teqeq r0, #0 /* Z &= running at address 0 */beq nand_load //-------------> go

#endif /* CONFIG_S3C2410_NAND_BOOT */

/*No.2 '***UART:mini-2440-uBoot***' */bl usart0_initbl usart0_send

relocate: /* relocate U-Boot to RAM */teq r0, #0 /* running at address 0 ? */bleq may_resume /* yes -> do low-level setup */adr r0, _start /* the above may have clobbered r0 */ldr r1, _TEXT_BASE /* test if we run from flash or RAM */cmp r0, r1 /* don t reloc during debug */beq done_relocateldr r2, _armboot_startldr r3, _bss_startsub r2, r3, r2 /* r2 <- size of armboot */add r2, r0, r2 /* r2 <- source end address */copy_loop:ldmia r0!, {r3-r10} /* copy from source address [r0] */stmia r1!, {r3-r10} /* copy to target address [r1] */cmp r0, r2 /* until source end address [r2] */ble copy_loop#ifndef CFG_NO_FLASHldr r0, _end_if_0 /* are we booting from NOR ? */cmp r0, r2ldreq r0, _booted_from_nor /* remember that we ve booted from */moveq r1, #1 /* NOR */streqb r1, [r0]

#endif /* !CFG_NO_FLASH */mov r0, #0 /* flush v3/v4 cache */mcr p15, 0, r0, c7, c7, 0ldr pc, _done_relocate /* jump to relocated code */

_done_relocate:.word done_relocate#ifdef CONFIG_S3C2410_NAND_BOOT

nand_load:bl usart0_initbl usart0_sendbl may_resume /* low-level setup and resume */@ reset NAND

#if defined(CONFIG_S3C2410)mov r1, #S3C2410_NAND_BASEldr r2, =0xf842 @ initial value enable tacls=3,rph0=6,rph1=0str r2, [r1, #oNFCONF]ldr r2, [r1, #oNFCONF]bic r2, r2, #0x800 @ enable chipstr r2, [r1, #oNFCONF]mov r2, #0xff @ RESET commandstrb r2, [r1, #oNFCMD]mov r3, #0 @ wait

1: add r3, r3, #0x1cmp r3, #0xablt 1b

2: ldr r2, [r1, #oNFSTAT] @ wait readytst r2, #0x1beq 2bldr r2, [r1, #oNFCONF]orr r2, r2, #0x800 @ disable chipstr r2, [r1, #oNFCONF]

#elif defined(CONFIG_S3C2440) || defined(CONFIG_S3C2442)mov r1, #S3C2440_NAND_BASEldr r2, =0xfff0 @ initial value tacls=3,rph0=7,rph1=7ldr r3, [r1, #oNFCONF]orr r3, r3, r2str r3, [r1, #oNFCONF]ldr r3, [r1, #oNFCONT]orr r3, r3, #1 @ enable nand controllerstr r3, [r1, #oNFCONT]

#endif /* CONFIG_S3C2440 || CONFIG_S3C2442 */ldr r0, _TEXT_BASE /* upper 128 KiB: relocated uboot */sub r0, r0, #CFG_MALLOC_LEN /* malloc area */sub r0, r0, #CFG_GBL_DATA_SIZE /* bdinfo */

#ifdef CONFIG_USE_IRQsub r0, r0, #(CONFIG_STACKSIZE_IRQ+CONFIG_STACKSIZE_FIQ)

#endifsub sp, r0, #12 /* leave 3 words for abort-stack */@ copy u-boot to RAMldr r0, _TEXT_BASEmov r1, #0x0mov r2, #CFG_UBOOT_SIZEbl nand_read_lltst r0, #0x0beq ok_nand_read

#ifdef CONFIG_DEBUG_LL

bad_nand_read:ldr r0, STR_FAILldr r1, SerBasebl PrintWord

1: b 1b @ infinite loop

#endifok_nand_read:

#ifdef CONFIG_DEBUG_LLldr r0, STR_OKldr r1, SerBasebl PrintWord

#endif@ verifymov r0, #0@ldr r1, =0x33f00000ldr r1, _TEXT_BASEmov r2, #0x400 @ 4 bytes * 1024 = 4K-bytes

go_next:ldr r3, [r0], #4ldr r4, [r1], #4teq r3, r4bne notmatchsubs r2, r2, #4beq done_nand_readbne go_next

notmatch:

#ifdef CONFIG_DEBUG_LLsub r0, r0, #4ldr r1, SerBasebl PrintHexWordldr r0, STR_FAILldr r1, SerBasebl PrintWord

#endif

1: b 1b

done_nand_read:ldr r0, _booted_from_nandmov r1, #1strb r1, [r0]

#endif /* CONFIG_S3C2410_NAND_BOOT */

done_relocate:#if defined(CONFIG_USE_IRQ) && (defined(CONFIG_S3C2410) || \defined(CONFIG_S3C2440) || defined(CONFIG_S3C2442))/* In the case of the S3C2410, if we ve somehow magically (JTAG, ...)ended up in RAM, then that ram is mapped to 0x30000000 and not 0.So we need to copy the interrupt vectors, etc. */mov r0, #0ldr r1, _TEXT_BASEmov r2, #0x40

irqvec_cpy_next:ldr r3, [r1], #4str r3, [r0], #4subs r2, r2, #4bne irqvec_cpy_next

#endif /* CONFIG_USE_IRQ */#endif /* CONFIG_SKIP_RELOCATE_UBOOT */

#endif/* Set up the stack */

stack_setup:ldr r0, _TEXT_BASE /* upper 128 KiB: relocated uboot */sub r0, r0, #CFG_MALLOC_LEN /* malloc area */sub r0, r0, #CFG_GBL_DATA_SIZE /* bdinfo */

#ifdef CONFIG_USE_IRQsub r0, r0, #(CONFIG_STACKSIZE_IRQ+CONFIG_STACKSIZE_FIQ)

#endifsub sp, r0, #12 /* leave 3 words for abort-stack */clear_bss:ldr r0, _bss_start /* find start of bss segment */ldr r1, _bss_end /* stop here */mov r2, #0x00000000 /* clear */clbss_l:str r2, [r0] /* clear loop... */add r0, r0, #4cmp r0, r1ble clbss_lldr pc, _start_armboot

/*go to uboot*/

_start_armboot: .word start_armboot/**************************************************************************** CPU_init_critical registers** setup important registers* setup memory timing***************************************************************************/#ifndef CONFIG_SKIP_LOWLEVEL_INIT

cpu_init_crit:/** flush v4 I/D caches*/mov r0, #0mcr p15, 0, r0, c7, c7, 0 /* flush v3/v4 cache */mcr p15, 0, r0, c8, c7, 0 /* flush v4 TLB *//** disable MMU stuff and caches*/mrc p15, 0, r0, c1, c0, 0bic r0, r0, #0x00002300 @ clear bits 13, 9:8 (--V- --RS)bic r0, r0, #0x00000087 @ clear bits 7, 2:0 (B--- -CAM)orr r0, r0, #0x00000002 @ set bit 2 (A) Alignorr r0, r0, #0x00001000 @ set bit 12 (I) I-Cachemcr p15, 0, r0, c1, c0, 0/** before relocating, we have to setup RAM timing* because memory timing is board-dependend, you will* find a lowlevel_init.S in your board directory.*/mov ip, lr

#if defined(CONFIG_AT91RM9200DK) || defined(CONFIG_AT91RM9200EK) || defined(CONFIG_AT91RM9200DF)#elsebl lowlevel_init

#endifmov lr, ipmov pc, lr

#endif /* CONFIG_SKIP_LOWLEVEL_INIT *//**************************************************************************** may_resume** Bring up memory and check if we re coming out of suspend.***************************************************************************/may_resume:mov r10, lr /* we may call cpu_init_crit *//* take sdram out of power down */ldr r0, =0x56000080 /* misccr */ldr r1, [ r0 ]bic r1, r1, #(S3C2410_MISCCR_nEN_SCLK0 | S3C2410_MISCCR_nEN_SCLK1 | S3C2410_MISCCR_nEN_SCLKE)str r1, [ r0 ]/* ensure signals stabalise */mov r1, #128

1: subs r1, r1, #1bpl 1b#if !defined(CONFIG_SKIP_LOWLEVEL_INIT) && defined(CONFIG_LL_INIT_NAND_ONLY)bl cpu_init_crit

#endif

#if defined(CONFIG_S3C2410) || defined(CONFIG_S3C2440) || defined(CONFIG_S3C2442)/* ensure some refresh has happened */ldr r1, =0xfffff

1: subs r1, r1, #1bpl 1b/* capture full EINT situation into gstatus 4 */ldr r0, =0x4A000000 /* SRCPND */ldr r1, [ r0 ]and r1, r1, #0xfldr r0, =0x560000BC /* gstatus4 */str r1, [ r0 ]ldr r0, =0x560000A8 /* EINTPEND */ldr r1, [ r0 ]ldr r0, =0xfff0and r1, r1, r0ldr r0, =0x560000BC /* gstatus4 */ldr r0, [ r0 ]orr r1, r1, r0ldr r0, =0x560000BC /* gstatus4 */str r1, [ r0 ]/* test for resume */ldr r1, =0x560000B4 /* gstatus2 */ldr r0, [ r1 ]tst r0, #0x02 /* is this resume from power down *//* well, if it was, we are going to jump to* whatever address we stashed in gstatus3,* and gstatus4 will hold the wake interrupt* source for the OS to look at*/ldrne pc, [r1, #4]

#endif /* CONFIG_S3C2410 || CONFIG_S3C244 || CONFIG_S3C2442 */

#endif /* CONFIG_SKIP_LOWLEVEL_INIT */mov pc, r10/**************************************************************************** Interrupt handling***************************************************************************/@

@ IRQ stack frame.

@

#define S_FRAME_SIZE 72#define S_OLD_R0 68

#define S_PSR 64

#define S_PC 60

#define S_LR 56

#define S_SP 52#define S_IP 48

#define S_FP 44

#define S_R10 40

#define S_R9 36

#define S_R8 32

#define S_R7 28

#define S_R6 24

#define S_R5 20

#define S_R4 16

#define S_R3 12

#define S_R2 8

#define S_R1 4

#define S_R0 0#define MODE_SVC 0x13

#define I_BIT 0x80/** use bad_save_user_regs for abort/prefetch/undef/swi ...* use irq_save_user_regs / irq_restore_user_regs for IRQ/FIQ handling*/.macro bad_save_user_regssub sp, sp, #S_FRAME_SIZEstmia sp, {r0 - r12} @ Calling r0-r12ldr r2, _armboot_startsub r2, r2, #(CONFIG_STACKSIZE+CFG_MALLOC_LEN)sub r2, r2, #(CFG_GBL_DATA_SIZE+8) @ set base 2 words into abort stackldmia r2, {r2 - r3} @ get pc, cpsradd r0, sp, #S_FRAME_SIZE @ restore sp_SVCadd r5, sp, #S_SPmov r1, lrstmia r5, {r0 - r3} @ save sp_SVC, lr_SVC, pc, cpsrmov r0, sp.endm.macro irq_save_user_regssub sp, sp, #S_FRAME_SIZEstmia sp, {r0 - r12} @ Calling r0-r12add r7, sp, #S_PCstmdb r7, {sp, lr}^ @ Calling SP, LRstr lr, [r7, #0] @ Save calling PCmrs r6, spsrstr r6, [r7, #4] @ Save CPSRstr r0, [r7, #8] @ Save OLD_R0mov r0, sp.endm.macro irq_restore_user_regsldmia sp, {r0 - lr}^ @ Calling r0 - lrmov r0, r0ldr lr, [sp, #S_PC] @ Get PCadd sp, sp, #S_FRAME_SIZEsubs pc, lr, #4 @ return & move spsr_svc into cpsr.endm.macro get_bad_stackldr r13, _armboot_start @ setup our mode stacksub r13, r13, #(CONFIG_STACKSIZE+CFG_MALLOC_LEN)sub r13, r13, #(CFG_GBL_DATA_SIZE+8) @ reserved a couple spots in abort stackstr lr, [r13] @ save caller lr / spsrmrs lr, spsrstr lr, [r13, #4]mov r13, #MODE_SVC @ prepare SVC-Mode@ msr spsr_c, r13msr spsr, r13mov lr, pcmovs pc, lr.endm.macro get_irq_stack @ setup IRQ stackldr sp, IRQ_STACK_START.endm.macro get_fiq_stack @ setup FIQ stackldr sp, FIQ_STACK_START.endm/** exception handlers*/.align 5

undefined_instruction:get_bad_stackbad_save_user_regsbl do_undefined_instruction.align 5

software_interrupt:get_bad_stackbad_save_user_regsbl do_software_interrupt.align 5

prefetch_abort:get_bad_stackbad_save_user_regsbl do_prefetch_abort.align 5

data_abort:get_bad_stackbad_save_user_regsbl do_data_abort.align 5

not_used:get_bad_stackbad_save_user_regsbl do_not_used#ifdef CONFIG_USE_IRQ.align 5

irq:get_irq_stackirq_save_user_regsbl do_irqirq_restore_user_regs.align 5

fiq:get_fiq_stack/* someone ought to write a more effiction fiq_save_user_regs */irq_save_user_regsbl do_fiqirq_restore_user_regs#else.align 5

irq:get_bad_stackbad_save_user_regsbl do_irq.align 5

fiq:get_bad_stackbad_save_user_regsbl do_fiq#endif#if 1#define PCLK 50625000 // cpu时钟是405MHz,所以PCLK=405000000/8

#define UART_CLK PCLK // UART0的时钟源设为PCLK

#define UART_BAUD_RATE 115200 // 波特率

#define UART_BRD ((UART_CLK / (UART_BAUD_RATE * 16)) - 1)

@ USART0相关寄存器定义

#define ULCON0 0X50000000 /*线路控制寄存器*/

#define UCON0 0X50000004 /*控制寄存器*/

#define UFCON0 0X50000008 /*FIFO 控制寄存器*/

#define UMCON0 0X5000000C /*MODEM 控制寄存器*/

#define UTRSTAT0 0x50000010 /*TX/RX 状态寄存器*/

#define UERSTAT0 0x50000014 /*Rx 错误状态寄存器*/

#define UFSTAT0 0x50000018 /*FIFO 状态寄存器*/

#define UMSTAT0 0x5000001C /*MODEM 状态寄存器*/

#define UTXH0_L 0x50000020 /*小端模式*/

#define UTXH0_B 0x50000023 /*大端模式*/

#define URXH0_L 0x50000024 /*小端模式*/

#define URXH0_B 0x50000027 /*大端模式*/

#define UBRDIV0 0x50000028 /*波特率分频寄存器 0*/ #define GPHCON 0x56000070 /*GPH控制寄存器*/

#define GPHUP 0x56000078 /*GPH内部上拉配置寄存器*//*usart0初始化*/usart0_init:

@串口IO初始化/**第4~7位设置 1010 ,把GPH2 GPH3引脚复用到usart0*/ldr r12,=GPHCONldr r11,[r12]bic r11,#0xf0orr r11,r11,#0xa0str r11,[r12]/**GPH2 GPH3 设置内部上拉 */ldr r12,=GPHUPldr r11,[r12]bic r11,#0xc0str r11,[r12]@8N1(8个数据位,无较验,1个停止位)ldr r11,=ULCON0ldr r12,= 0x03str r12,[r11]

@查询方式,UART时钟源为PCLKldr r11,=UCON0ldr r12,= 0x05str r12,[r11]

@不使用FIFOldr r11,=UFCON0ldr r12,= 0x00str r12,[r11]

@不使用流控制ldr r11,=UMCON0ldr r12,= 0x00str r12,[r11]

@波特率设置为115200ldr r11,=UBRDIV0ldr r12,=UART_BRDstr r12,[r11]mov pc,lr@usart0发送测试

usart0_send:ldr r12,=UTXH0_Lldr r11,='\n'str r11,[r12]ldr r11,='*'str r11,[r12]ldr r11,='*'str r11,[r12]ldr r11,='*'str r11,[r12]ldr r11,='U'str r11,[r12]ldr r11,='A'str r11,[r12]ldr r11,='R'str r11,[r12]ldr r11,='T'str r11,[r12]ldr r11,=':'str r11,[r12]ldr r11,='m'str r11,[r12]ldr r11,='i'str r11,[r12] ldr r11,='n'str r11,[r12] ldr r11,='i'str r11,[r12]ldr r11,='-'str r11,[r12]ldr r11,='2'str r11,[r12]ldr r11,='4'str r11,[r12]ldr r11,='4'str r11,[r12]ldr r11,='0'str r11,[r12]ldr r11,='-'str r11,[r12]ldr r11,='u'str r11,[r12]ldr r11,='B'str r11,[r12]ldr r11,='o'str r11,[r12]ldr r11,='o'str r11,[r12]ldr r11,='t'str r11,[r12]ldr r11,='*'str r11,[r12]ldr r11,='*'str r11,[r12]ldr r11,='*'str r11,[r12]ldr r11,='\n'str r11,[r12]mov pc,lr@检查usart0是否发送完成,未完成则等待

check_tx_flag:ldr r1,=UTRSTAT0ldr r0,[r1]tst r0,#4beq check_tx_flagmov pc,lr@打印r10寄存器数据

usart0_print_r10: mov r11, #0x1 @循环4次,每次打印一字节数据0:@发送一字节数据ldr r12,=UTXH0_LMOV R10, R10, ROR #24 @循环右移24位str r10,[r12] @一次发生8bit数据mov r1,lr @保存lrbl check_tx_flag @等待发送完成(这里会改变lr)mov lr,r1 @恢复lr@判断循环是否结束sub r11, r11, #1mov r12, #0cmp r11, r12bne 0bmov pc,lr //返回被调用的地方#endif

串口代码

#if 1#define PCLK 50625000 // cpu时钟是405MHz,所以PCLK=405000000/8

#define UART_CLK PCLK // UART0的时钟源设为PCLK

#define UART_BAUD_RATE 115200 // 波特率

#define UART_BRD ((UART_CLK / (UART_BAUD_RATE * 16)) - 1)

@ USART0相关寄存器定义

#define ULCON0 0X50000000 /*线路控制寄存器*/

#define UCON0 0X50000004 /*控制寄存器*/

#define UFCON0 0X50000008 /*FIFO 控制寄存器*/

#define UMCON0 0X5000000C /*MODEM 控制寄存器*/

#define UTRSTAT0 0x50000010 /*TX/RX 状态寄存器*/

#define UERSTAT0 0x50000014 /*Rx 错误状态寄存器*/

#define UFSTAT0 0x50000018 /*FIFO 状态寄存器*/

#define UMSTAT0 0x5000001C /*MODEM 状态寄存器*/

#define UTXH0_L 0x50000020 /*小端模式*/

#define UTXH0_B 0x50000023 /*大端模式*/

#define URXH0_L 0x50000024 /*小端模式*/

#define URXH0_B 0x50000027 /*大端模式*/

#define UBRDIV0 0x50000028 /*波特率分频寄存器 0*/ #define GPHCON 0x56000070 /*GPH控制寄存器*/

#define GPHUP 0x56000078 /*GPH内部上拉配置寄存器*//*usart0初始化*/usart0_init:

@串口IO初始化/**第4~7位设置 1010 ,把GPH2 GPH3引脚复用到usart0*/ldr r12,=GPHCONldr r11,[r12]bic r11,#0xf0orr r11,r11,#0xa0str r11,[r12]/**GPH2 GPH3 设置内部上拉 */ldr r12,=GPHUPldr r11,[r12]bic r11,#0xc0str r11,[r12]@8N1(8个数据位,无较验,1个停止位)ldr r11,=ULCON0ldr r12,= 0x03str r12,[r11]

@查询方式,UART时钟源为PCLKldr r11,=UCON0ldr r12,= 0x05str r12,[r11]

@不使用FIFOldr r11,=UFCON0ldr r12,= 0x00str r12,[r11]

@不使用流控制ldr r11,=UMCON0ldr r12,= 0x00str r12,[r11]

@波特率设置为115200ldr r11,=UBRDIV0ldr r12,=UART_BRDstr r12,[r11]mov pc,lr@usart0发送测试

usart0_send:ldr r12,=UTXH0_Lldr r11,='\n'str r11,[r12]ldr r11,='*'str r11,[r12]ldr r11,='*'str r11,[r12]ldr r11,='*'str r11,[r12]ldr r11,='U'str r11,[r12]ldr r11,='A'str r11,[r12]ldr r11,='R'str r11,[r12]ldr r11,='T'str r11,[r12]ldr r11,=':'str r11,[r12]ldr r11,='m'str r11,[r12]ldr r11,='i'str r11,[r12] ldr r11,='n'str r11,[r12] ldr r11,='i'str r11,[r12]ldr r11,='-'str r11,[r12]ldr r11,='2'str r11,[r12]ldr r11,='4'str r11,[r12]ldr r11,='4'str r11,[r12]ldr r11,='0'str r11,[r12]ldr r11,='-'str r11,[r12]ldr r11,='u'str r11,[r12]ldr r11,='B'str r11,[r12]ldr r11,='o'str r11,[r12]ldr r11,='o'str r11,[r12]ldr r11,='t'str r11,[r12]ldr r11,='*'str r11,[r12]ldr r11,='*'str r11,[r12]ldr r11,='*'str r11,[r12]ldr r11,='\n'str r11,[r12]mov pc,lr@检查usart0是否发送完成,未完成则等待

check_tx_flag:ldr r1,=UTRSTAT0ldr r0,[r1]tst r0,#4beq check_tx_flagmov pc,lr@打印r10寄存器数据

usart0_print_r10: mov r11, #0x1 @循环4次,每次打印一字节数据0:@发送一字节数据ldr r12,=UTXH0_LMOV R10, R10, ROR #24 @循环右移24位str r10,[r12] @一次发生8bit数据mov r1,lr @保存lrbl check_tx_flag @等待发送完成(这里会改变lr)mov lr,r1 @恢复lr@判断循环是否结束sub r11, r11, #1mov r12, #0cmp r11, r12bne 0bmov pc,lr //返回被调用的地方#endif Supported machines are: popt->name:M

Supported machines are: popt->name:m

Supported machines are: popt->name:kernel

Supported machines are: popt->name:serial

Supported machines are: popt->name:mtdblock

Supported machines are:MTD_ALIAS

Supported machines are: popt->name:usb

Supported machines are: popt->name:usbdevice

Supported machines are: popt->name:usbdevice

Supported machines are: popt->name:show-cursor

Supported machines are: popt->name:net

Supported machines are: popt->name:net

Supported machines are: popt->name:monitor

Supported machines: ram_size:128 MB

[leelong]-> mini2440_init: Boot mode: NAND,nor_idx:-1,nand_idx:0

S3C: CLK=240 HCLK=240 PCLK=240 UCLK=57

QEMU: ee24c08_init

DM9000: INIT QEMU MAC : 52:54:00:12:34:56

mini2440_init: nand_init(NAND_MFR_SAMSUNG, nand_cid)=(0xec,0x76)

pflash_cfi02_register: start

pflash_cfi02_register: end

mini2440_init: file too big (2MBytes),pflash_cfi02_register

QEMU mini2440_reset: loaded default u-boot from NAND

QEMU mini2440_reset: loaded override u-boot (size 3ae00)

QEMU mini2440_reset: lee loaded uImage (size 234000)

QEMU mini2440_reset:**welcome to uboot's world,start your Fuck codes**

***UART:mini-2440-uBoot******UART:mini-2440-uBoot***

<uboot> <uboot> ./board/mini2440/mini2440.c board_init

S3C: CLK=240 HCLK=60 PCLK=30 UCLK=57

S3C: CLK=240 HCLK=60 PCLK=30 UCLK=48

S3C: CLK=405 HCLK=101 PCLK=50 UCLK=48

U-Boot 1.3.2-mini2440 (Jun 19 2024 - 00:23:30)CPUID: 32440001

FCLK: 405 MHz

HCLK: 101.250 MHz

PCLK: 50.625 MHz

I2C: ready

<uboot> ./board/mini2440/mini2440.c dram_init dram:128 MiB,mem->BANKCON[6] = 0x00018002

<uboot> ./board/mini2440/mini2440.c dram_init dram:128 MiB,mem->BANKCON[7] = 0x00018002

DRAM: 256 MB

<uboot> Nor flash...<uboot> ./board/mini2440/flash.c flash_init

Nor Flash: 2 MB

<uboot> NAND flash...cpu/arm920t/s3c24x0/nand64m.c,board_nand_init()**<uboot> busw:0,maf_id:0xec,dev_id:0x76

**<uboot> busw:0,maf_name:Samsung,maf_id:0xec,dev_id:0x76

Bad block table not found for chip 0

Bad block table not found for chip 0

<uboot> <uboot> ./drivers/mtd/nand/nand.c

<uboot> <uboot> nand:64 MiB

*** Warning - bad CRC or NAND, using default environmentUSB: S3C2410 USB Deviced

In: serial

Out: serial

Err: serial

MAC: 08:08:11:18:12:27

<uboot> mtdparts default <<<< ...<uboot> mtdparts default >>>> ...

Hit any key to stop autoboot: 0

MINI2440 #

相关文章:

)

Mini2440 start.s 修改支持串口输出,方便调试 (四)

经常会遇到点板子的时候,板子没有任何反应!怎么知道板子有没有在正常启动,在uboot阶段 start.s 中加入串口打印信息是很有必要的! 输出串口信息 ***UART:mini-2440-uBoot*** ***UART:mini-2440-uBoot*** ***UART:mini-2440-uBoo…...

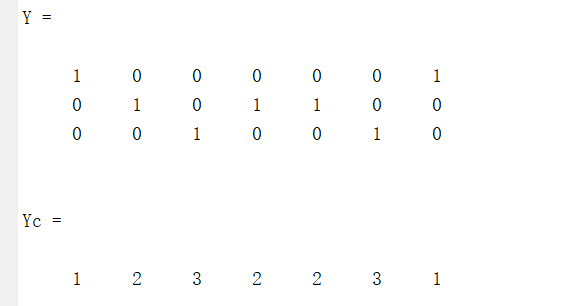

【教程】几种不同的RBF神经网络

本站原创文章,转载请说明来自《老饼讲解-机器学习》www.bbbdata.com 目录 一、经典RBF神经网络1.1.经典径向基神经网络是什么1.2.经典径向基神经网络-代码与示例 二、广义回归神经网络GRNN2.1.广义回归神经网络是什么2.2.广义回归神经网络是什么-代码与示例 三、概率…...

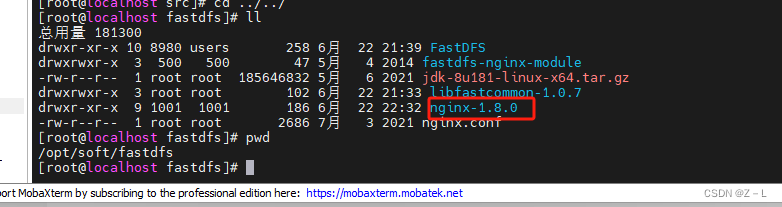

【Liunx-后端开发软件安装】Liunx安装FDFS并整合nginx

【Liunx-后端开发软件安装】Liunx安装nacos 文章中涉及的相关fdfs相关软件安装包请点击下载: https://download.csdn.net/download/weixin_49051190/89471122 一、简介 FastDFS是一个开源的轻量级分布式文件系统,它对文件进行管理,功能包括…...

【Java笔记】Flyway数据库管理工具的基本原理

文章目录 1. 工作流程2. 版本号校验算法3. 锁机制3.1 为什么数据库管理工具需要锁3.2 flyway的锁机制 Reference 最近实习做的几个项目都用到了Flyway来做数据库的版本管理,顺便了解了下基本原理,做个记录。 详细的使用就不写了,网上教程很多…...

国际数字影像产业园创业培训,全面提升创业能力!

国际数字影像产业园作为数字影像产业的创新高地,致力于提供全面的创业支持服务。其中,创业培训作为重要的组成部分,旨在通过系统的课程设置和专业的讲师团队,为创业者提供从基础到进阶的全方位指导,帮助他们在数字影像…...

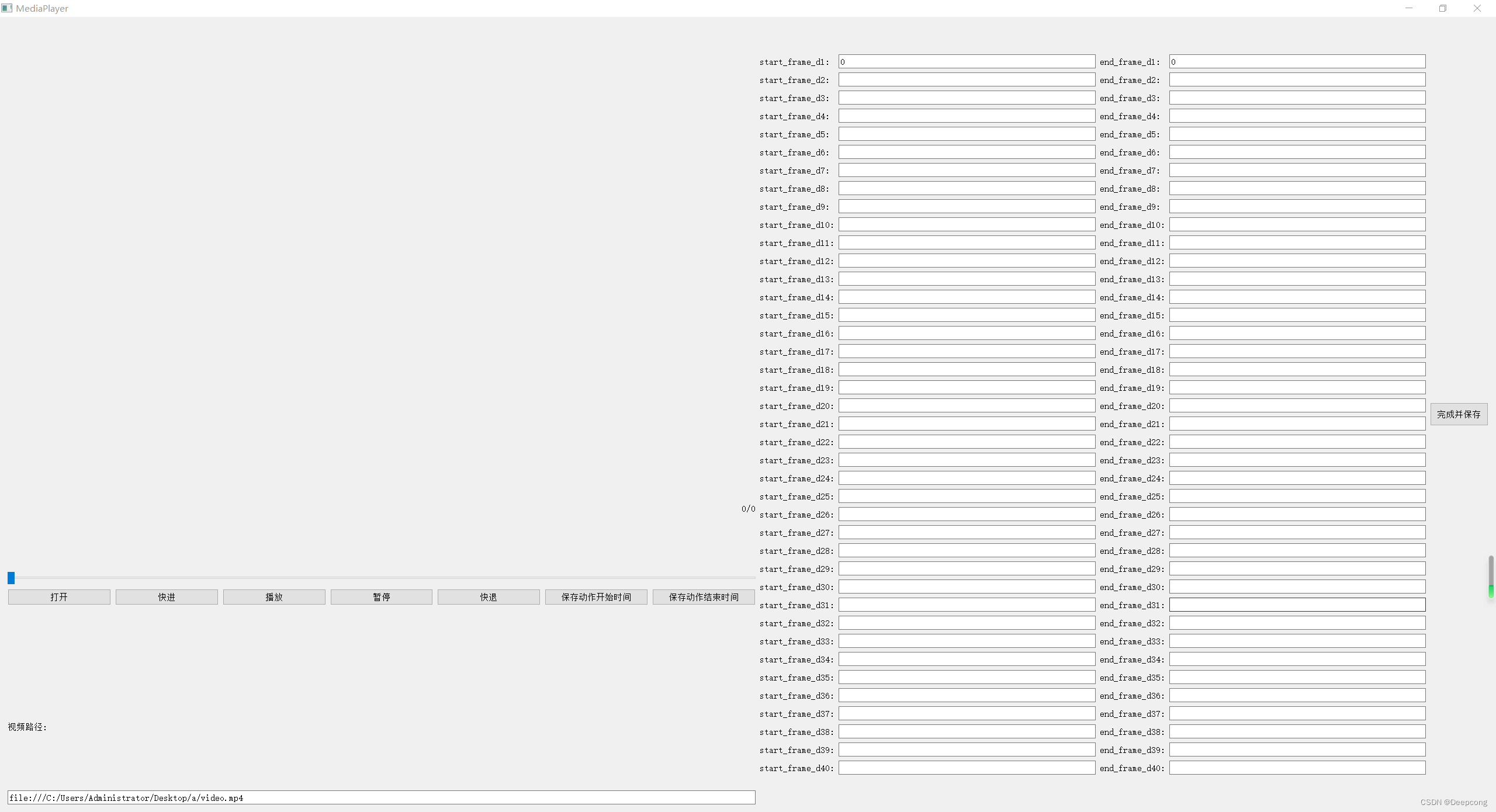

pyqt5 制作视频剪辑软件,切割视频

该软件用于切割视频,手动选取视频片段的起始帧和结束帧并保存为json文件。gui界面如下:包含快进、快退、暂停等功能, 代码如下: # codingUTF-8 """ theme: pyqt5实现动作起始帧和结束帧的定位,将定位到…...

VUE----通过nvm管理node版本

使用 NVM(Node Version Manager)来管理和切换 Node.js 版本是一个很好的选择。以下是在 苹果电脑macos系统 上使用 NVM 安装和切换 Node.js 版本的步骤: 1. 安装 NVM 如果你还没有安装 NVM,可以按照以下步骤进行安装:…...

R语言进行字符的替换和删减gsub,substr函数

目录 R语言读文件“-“变成“.“ 提取列字符前几个 提取列字符末尾几个 进行字母替换 paste0函数使用 长宽数据转换 R语言读文件“-“变成“.“ R语言读文件“-“变成“.“_r语言 列名中的-变成了点-CSDN博客 怎样将"."还原为"-" rm(list = ls()…...

2024年6月27日,欧盟REACH法规新增第31批1项SVHC高关注物质

ECHA公布第31批1项SVHC,物质已增至241项 2024年6月27日,ECHA公布第31批1项SVHC,总数达241项。新增物质未包括磷酸三苯酯,仍在评议中。REACH法规要求SVHC含量超0.1%需告知下游,出口超1吨须通报ECHA。SCIP通报要求SVHC含…...

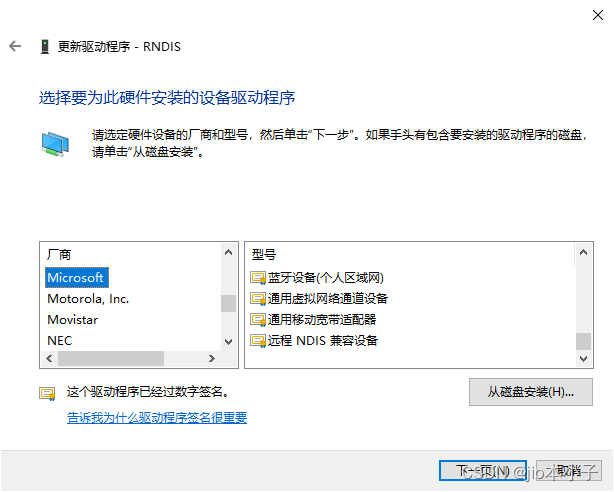

高通410-linux棒子设置网络驱动

1.首先打开设备管理器 2.看到其他设备下的RNDIS,右键更新驱动程序 3.点击浏览我的电脑… 最后一个...

PostgreSQL的系统视图pg_stat_archiver

PostgreSQL的系统视图pg_stat_archiver 在 PostgreSQL 数据库中,pg_stat_archiver 视图提供了关于归档进程(archiver process)的统计信息。归档进程负责将 WAL(Write-Ahead Logging)日志文件复制到归档存储࿰…...

【D3.js in Action 3 精译】第一部分 D3.js 基础知识

第一部分 D3.js 基础知识 欢迎来到 D3.js 的世界!可能您已经迫不及待想要构建令人惊叹的数据可视化项目了。我们保证,这一目标很快就能达成!但首先,我们必须确保您已经掌握了 D3.js 的基础知识。这一部分提到的概念将会在您后续的…...

)

面试经验分享 | 渗透测试工程师(实习岗)

所面试的公司:某安全厂商 所在城市:南京 面试职位:渗透测试工程师实习岗位 面试过程: 腾讯会议(视频) 面试过程:整体流程就是自我介绍加上一些问题问题balabalabala。。。由于面的岗位是渗透…...

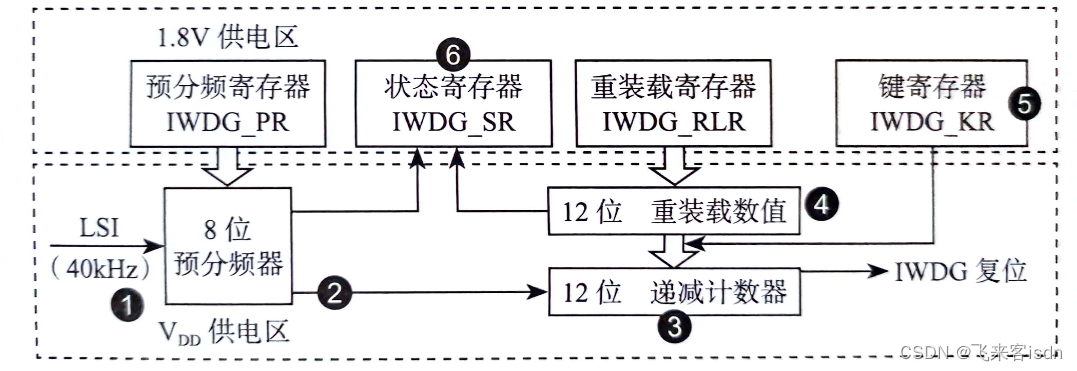

STM32 IWDG(独立看门狗)

1 IWDG简介 STM32有两个看门狗:一个是独立看门狗(IWDG),另外一个是窗口看门狗。独立看门狗也称宠物狗,窗口看门狗也称警犬。本文主要分析独立看门狗的功能和它的应用。 独立看门狗用通俗一点的话来解释就是一个12位的…...

ios swift5 获取wifi列表

参考博客: iOS之Wifi开发探究 - 稀土掘金 iOS 无法获取 WiFi 列表?一定是因为你不知道这个框架 - 稀土掘金 iOS获取Wifi列表详解 - 简书...

回溯法c++学习 解决八皇后问题

使用回溯法解决八皇后问题 八皇后问题是一个以国际象棋为背景的问题:如何能够在88 的国际象棋棋盘上放置八个皇后,使得任何一个皇后都无法直接吃掉其他的皇后?为了达到此目的,任两个皇后都不能处于同一条横行、纵行或斜线上。这…...

5. Spring IoCDI ★ ✔

5. Spring IoC&DI 1. IoC & DI ⼊⻔1.1 Spring 是什么?★ (Spring 是包含了众多⼯具⽅法的 IoC 容器)1.1.1 什么是容器?1.1.2 什么是 IoC?★ (IoC: Inversion of Control (控制反转))总…...

数据库自动备份到gitee上,实现数据自动化备份

本人有个不太好的习惯,每次项目的数据库都是在线上创建,Navicat 连接线上数据库进行处理,最近有一个项目需要二次升级,发现老项目部署的服务器到期了,完蛋,数据库咩了!!!…...

探索 Spring Cloud Gateway:构建微服务架构的关键一环

1. 简介 在当今的分布式系统中,微服务架构已经成为了一种流行的架构模式。在微服务架构中,服务被拆分为小型、可独立部署的服务单元,这些服务单元能够通过网络互相通信,形成一个整体的应用系统。然而,随着微服务数量的…...

P1114 “非常男女”计划最优解

原题地址 P1114 “非常男女”计划 - 洛谷 | 计算机科学教育新生态 (luogu.com.cn) 代码题解 AC代码(1) 因为用的是级的算法,所以最后一个 了,这里使用特判来得到的,给你们放一下代码: #include <bi…...

说说你对spring的IOC的理解

面试 IOC指的就是控制反转,指的就是创建对象的控制权的转移,简单来说,由之前的手动new对象,转换成了由spring自动生产,spring利用java的反射机制,根据配置文件或注解在运行时动态创建并管理对象。...

终极对比指南:Autoenv vs 其他环境管理工具,如何选择最适合你的目录环境自动化方案

终极对比指南:Autoenv vs 其他环境管理工具,如何选择最适合你的目录环境自动化方案 【免费下载链接】autoenv Directory-based environments. 项目地址: https://gitcode.com/gh_mirrors/au/autoenv Autoenv是一款强大的目录环境自动化工具&#…...

高效实现Windows任务栏个性化的5个极简方案:轻量级透明化工具TranslucentTB全指南

高效实现Windows任务栏个性化的5个极简方案:轻量级透明化工具TranslucentTB全指南 【免费下载链接】TranslucentTB A lightweight utility that makes the Windows taskbar translucent/transparent. 项目地址: https://gitcode.com/gh_mirrors/tr/TranslucentTB …...

微软服软!被骂5年的Win11将被“整改”:告别强制更新、减少Copilot、任务栏摆放自由

整理 | 屠敏出品 | CSDN(ID:CSDNnews)Windows 11 自 2021 年发布以来,因任务栏功能缩水、UI 不统一、强制网络登录以及更高的硬件门槛,成为用户集中吐槽的焦点。再加上近来微软猛推 AI 功能,Copilot 的入口…...

【GNSS定位原理及算法杂记2】GNSS观测量:从捕获到解算,揭秘接收机内部信号处理链路

1. GNSS观测量:定位技术的三大支柱 当你打开手机地图查看自己的位置时,背后是GNSS接收机在默默工作。它通过处理来自太空卫星的信号,最终计算出你所在的位置。这个过程中最关键的就是三种观测量:伪距、载波相位和多普勒频移。这三…...

)

Axure RP 10实战:3分钟搞定Tab切换效果(附交互样式设置技巧)

Axure RP 10高级Tab切换效果:从基础实现到专业级交互设计 在当今快节奏的数字化产品设计领域,Tab切换作为最常见的用户界面元素之一,其交互体验的优劣直接影响用户对产品的第一印象。Axure RP 10作为行业领先的原型设计工具,提供了…...

用Mermaid Live Editor 5分钟搞定技术图表:从零开始的完整实战指南

用Mermaid Live Editor 5分钟搞定技术图表:从零开始的完整实战指南 【免费下载链接】mermaid-live-editor Edit, preview and share mermaid charts/diagrams. New implementation of the live editor. 项目地址: https://gitcode.com/GitHub_Trending/me/mermaid…...

免费降AI vs 付费降AI:省下的钱够不够你重新查重?

选降AI工具这件事,我前后折腾了大半个月。起因很简单:论文用DeepSeek写了初稿,知网一查AI率直接飙到90%多,导师让我三天内搞定。 先说结论:免费降AI率工具能用,但别指望它帮你一步到位。 我试了五六个免费…...

的演进:从游戏行业到供应链攻击的AI应用)

APT41 (Barium) 的演进:从游戏行业到供应链攻击的AI应用

前言 1. 技术背景 —— 这个技术在攻防体系中的位置 高级持续性威胁 (Advanced Persistent Threat, APT) 是网络攻防体系金字塔的顶端。它并非指某种单一技术,而是一个复杂的、有组织的、长期的网络攻击活动集合。在整个攻防图谱中,APT代表着最高级别的对…...

多平台网络资源捕获工具:突破下载限制的技术实现与场景化应用

多平台网络资源捕获工具:突破下载限制的技术实现与场景化应用 【免费下载链接】res-downloader 资源下载器、网络资源嗅探,支持微信视频号下载、网页抖音无水印下载、网页快手无水印视频下载、酷狗音乐下载等网络资源拦截下载! 项目地址: https://gitc…...