米联客-FPGA程序设计Verilog语法入门篇连载-16 Verilog语法_时钟分频设计

软件版本:无

操作系统:WIN10 64bit

硬件平台:适用所有系列FPGA

板卡获取平台:https://milianke.tmall.com/

登录“米联客”FPGA社区 http://www.uisrc.com 视频课程、答疑解惑!

1概述

本小节讲解Verilog语法的时钟分频设计,需要掌握时钟的特性,以及如何进行时钟分频设计。

2时钟分频

在FPGA的硬件电路设计中,PCB板上需要有时钟产生源,常见的外部时钟源有RC/LC 振荡电路,无源/有源晶体振荡器,利用石英晶体的压电效应产生谐振信号。此类时钟源频率精度高,稳定性好,噪声低,温漂小。有源晶振中,往往还加入了压控或温度补偿,时钟的相位和频率都有较好的特性。

有时我们在时序电路设计中,有些模块工作频率会低于外部时钟频率,此时就需要对时钟进行一定的分频得到频率较低的时钟。在FPGA内部常常存在一定的PLL(锁相环,Phase Locked Loop)资源,它可以对时钟进行分频或者倍频的操作。

本小节主要介绍如何使用寄存器等资源实现时钟偶数分频、奇数分频和小数分频的。

2.1 偶数分频

偶数分频直接使用寄存器进行取反操作,可以得到二分频、四分频、六分频、八分频等,且占空比是50%。例:

module even_div(input rst_n, //输入复位input clk, //输入时钟output clk_div //分频时钟);parameter DIV_NUM = 6; //分频参数reg [15:0] clk_cnt;reg clk_out;always @(posedge clk or negedge rst_n)beginif (!rst_n)beginclk_cnt <= 'b0 ;endelse if(clk_cnt == ((DIV_NUM/2) -1)) beginclk_cnt <= 'b0;endelsebeginclk_cnt <= clk_cnt + 1'b1; //分频计数器end endalways @(posedge clk or negedge rst_n)beginif (!rst_n)beginclk_out <= 'b0 ;endelse if(clk_cnt == ((DIV_NUM/2) -1)) //计数到分频参数的一半beginclk_out <= ~clk_out; //产生翻转endelsebeginclk_out <= clk_out; //否则保持不变end endassign clk_div = clk_out;endmodule

2.2 奇数分频

如果奇数分频不要求占空比是50%,可以按照类似的偶数分频进行处理。如果奇数分频要求占空比是50%,我们以三分频为例进行讲解如何进行奇数分频。

时序如图所示:

例:

module odd_div(input rst_n,input clk,output clk_div);parameter DIV_NUM = 3;reg [15:0] clk_cnt;reg clk_out;reg clk_div_1;reg clk_div_2;always @(posedge clk or negedge rst_n)beginif (!rst_n)beginclk_cnt <= 'b0;endelse if(clk_cnt == (DIV_NUM - 1)) //产生计数beginclk_cnt <= 'b0; //clk_cnt清零复位endelsebeginclk_cnt <= clk_cnt + 1'b1; //clk_cnt为0、1、2end endalways @(posedge clk or negedge rst_n) //clk上升沿触发beginif (!rst_n)beginclk_div_1 <= 1'b0;endelse if (clk_cnt == (DIV_NUM >> 1)-1 ) //clk_cnt 为0时,clk_div_1为0begin clk_div_1 <= 1'b0;endelse if (clk_cnt == DIV_NUM-1) //clk_cnt 为2时,clk_div_1为1begin clk_div_1 <= 1'b1;endelse begin clk_div_1 <= clk_div_1; //clk_cnt 为2时,clk_div_1为0end endalways @(negedge clk or negedge rst_n) //clk下降沿触发beginif (!rst_n)beginclk_div_2 <= 1'b0;endelse if (clk_cnt == (DIV_NUM >> 1)-1 ) //clk_cnt 为0时,clk_div_1为0begin clk_div_2 <= 1'b0;endelse if (clk_cnt == DIV_NUM-1) //clk_cnt 为2时,clk_div_1为1begin clk_div_2 <= 1'b1;endelse begin clk_div_2 <= clk_div_2;end endassign clk_div = clk_div_1 | clk_div_2 ; //clk_div_1与clk_div_2产生三分频时钟endmodule

2.3 小数分频

使用Verilog不能进行精确的小数分频,但是可以在长时间内达到的平均频率接近小数分频的频率。

举例说明使用平均频率求解小数分频的方法,例如进行6.7倍分频,需要保证源时钟67个周期的时间等于分频时钟10个周期的时间即可。此时需要在67个源时钟周期内进行3次6分频,7次7分频。

具体的实现过程如下:

当进行分频时考虑67个源时钟周期需要进行10次分频,即需要3次每6个周期进行分频和7次每7个周期进行分频,即完了6.7倍分频。我们进行分频时需要将两个分频进行穿插交替,不能一直按照一种倍数频率进行分频,否则会造成相位抖动过大。

如何决定分频的前后顺序呢?我们根据差值进行比较来选择相应的分频倍数,具体过程如下:

- 第一次进行分频,67 – 10*6 = 7 < 10 ,第一次进行6分频。

- 第二次进行分频,加上上次的7+7 =14 >= 10,第二次进行7分频。

- 第三次进行分频,加上上次的7+4 =11 >= 10,第三次进行7分频。

- 第四次进行分频,加上上次的7+1 =8< 10 , 第四次进行6分频。

- 第五次进行分频,加上上次的7+8=15 >= 10,第五次进行7分频。

- 第六次进行分频,加上上次的7+5 =12 >= 10 , 第六次进行7分频。

- 第七次进行分频,加上上次的7+2=9 < 10,第七次进行6分频。

- 第八次进行分频,加上上次的7+9=16 >= 10,第八次进行7分频。

- 第九次进行分频,加上上次的7+6=13 >= 10,第九次进行7分频。

- 第十次进行分频,加上上次的7+3=10 >= 10,第十次进行7分频。

例:

module frac_div(input rst_n ,input clk,output reg clk_div);parameter SOURCE_NUM = 67;parameter DEST_NUM = 10;parameter SOURCE_DIV = SOURCE_NUM/DEST_NUM;parameter DEST_DIV = SOURCE_DIV + 1;parameter DIFF_ADD = SOURCE_NUM - SOURCE_DIV*DEST_NUM;reg [7:0] cnt_end_num;reg [7:0] div_cnt; wire[7:0] diff_cnt;reg [7:0] diff_cnt_ff;wire diff_cnt_en;always @(posedge clk or negedge rst_n)beginif (!rst_n)begindiv_cnt <= 'b0 ;clk_div <= 1'b0 ;endelse if (div_cnt == cnt_end_num)begindiv_cnt <= 'b0 ;clk_div <= 1'b1 ;endelse begindiv_cnt <= div_cnt + 1'b1 ;clk_div <= 1'b0 ;endendassign diff_cnt_en = div_cnt == cnt_end_num ;assign diff_cnt = diff_cnt_ff >= DEST_NUM ?diff_cnt_ff -10 + DIFF_ADD :diff_cnt_ff + DIFF_ADD ; always @(posedge clk or negedge rst_n)beginif (!rst_n)begindiff_cnt_ff <= 0 ;endelse if (diff_cnt_en)begindiff_cnt_ff <= diff_cnt ;endendalways @(posedge clk or negedge rst_n)beginif (!rst_n)cnt_end_num <= SOURCE_DIV-1 ;else if (diff_cnt >= 10)cnt_end_num <= DEST_DIV-1 ;elsecnt_end_num <= SOURCE_DIV-1 ;endendmodule

如果对时钟精度等要求比较高建议使用PLL进行分频。

相关文章:

米联客-FPGA程序设计Verilog语法入门篇连载-16 Verilog语法_时钟分频设计

软件版本:无 操作系统:WIN10 64bit 硬件平台:适用所有系列FPGA 板卡获取平台:https://milianke.tmall.com/ 登录“米联客”FPGA社区 http://www.uisrc.com 视频课程、答疑解惑! 1概述 本小节讲解Verilog语法的时钟…...

【Echarts】custom自定义图表实现甘特图

效果图 主要注意点: 1、右上角图例visualMap实现 2、visualMap增加formatter 3、series使用custom自定义图表,encode解析四维数组。核心是renderItem方法,必填项,且需要注意要全部定义在options里面!!&…...

)

【高等代数笔记】003线性方程组的解法(一)

1. 线性方程组的解法 1.1 解线性方程组的矩阵消元法 【例1】解线性方程组 { x 1 3 x 2 x 3 2 3 x 1 4 x 2 2 x 3 9 − x 1 − 5 x 2 4 x 3 10 2 x 1 7 x 2 x 3 1 \left\{\begin{array}{ll} x_{1}3x_{2}x_{3}2 \\ 3x_{1}4x_{2}2x_{3}9 \\ -x_{1}-5x_{2}4x_{3}10 \\…...

Scrapy入门教程

Scrapy入门教程:打造高效爬虫的第一步 1. 引言 在当今的网络世界中,信息是无价的资源。而爬虫工具则是获取这些资源的有力武器。Scrapy 是 Python 生态系统中最强大的爬虫框架之一,它不仅功能强大,而且易于扩展,适用…...

Microsoft VBA Excel VBA学习笔记——双重筛选+复制数值1.0

问题场景 CountryProductCLASS 1CLASS 2CLASS 3CLASS 4CLASS 5CLASS 6…USApple0.3641416030.8918210610.0591451990.7320110290.0509636560.222464259…USBanana0.2300833330.4027262180.1548836670.2988904860.7802326210.028592635…CNApple0.7762370470.5075548320.481978…...

谷歌反垄断官司败诉后,或又面临被拆分风险?

KlipC报道:上周8月5日,美国法院裁定谷歌的搜索业务违反了美国反垄断法,非法垄断在线搜索和搜索文本广告市场。据悉,胜诉的美国司法部正在考虑拆分谷歌。其他选项包括强制谷歌与竞争对手分享更多数据,以及防止其在人工智…...

数据结构入门——06树

1.树 树(Tree)非线性数据结构,它是n(n≥0)个节点的有限集合,它满足两个条件 : 有且仅有一个特定的称为根(Root)的节点; 其余的节点可以分为m(m…...

FFmpeg源码:av_packet_move_ref、av_packet_make_refcounted函数分析

一、av_packet_move_ref函数 (一)av_packet_move_ref函数的声明 av_packet_move_ref函数声明在FFmpeg源码(本文演示用的FFmpeg源码版本为7.0.1)的头文件libavcodec/packet.h中: /*** Move every field in src to ds…...

12 中断

12 中断 1、内核中断编程2、顶半部和底半部机制2.1 任务的相关概念2.1.1 分类2.1.2 优先级2.1.3 进程调度2.1.4 休眠sleep 2.2 顶半部和底半部实现机制2.2.1 顶半部特点2.2.2 底半部特点2.2.3 底半部实现方法之:tasklet2.2.4 底半部实现机制之工作队列2.2.5 底半部实现机制之软…...

经典算法题总结:十大排序算法,外部排序和Google排序简介

十大排序算法 就地性:顾名思义,原地排序通过在原数组上直接操作实现排序,无须借助额外的辅助数组,从而节省内存。通常情况下,原地排序的数据搬运操作较少,运行速度也更快。 稳定性:稳定排序在完…...

服务器是什么?怎么选择适合自己的服务器?

在这个数字化的世界中,我们每天都在与各种网站打交道,浏览新闻、购物、看视频等。你是否曾经好奇过,这些网站是如何运行的?它们又是如何实现随时随地可访问的呢? 在这背后,有一个神秘的角色在默默地支撑着…...

区块链技术的应用场景

区块链技术是一种分布式数据库或公共分类账的形式,它保证了数据的完整性和透明性。它最初是为了支持比特币这种加密货币而被发明的,但现在已经被广泛应用于多种领域,包括供应链管理、投票系统、数字身份验证等。 基本概念 区块 (Block) 区块…...

凤凰端子音频矩阵应用领域

凤凰端子音频矩阵,作为一种集成了凤凰端子接口的音频矩阵设备,具有广泛的应用领域。以下是其主要应用领域: 一、专业音响系统 会议系统:在会议室中,凤凰端子音频矩阵能够处理多个话筒和音频源的信号,实现…...

LeetCode-字母异位词分组

题目描述 给你一个字符串数组,请你将 字母异位词 组合在一起。可以按任意顺序返回结果列表。 字母异位词 是由重新排列源单词的所有字母得到的一个新单词。 示例 1: 输入: strs ["eat", "tea", "tan", "ate", "na…...

《Linux运维总结:基于x86_64架构CPU使用docker-compose一键离线部署etcd 3.5.15容器版分布式集群》

总结:整理不易,如果对你有帮助,可否点赞关注一下? 更多详细内容请参考:《Linux运维篇:Linux系统运维指南》 一、部署背景 由于业务系统的特殊性,我们需要面对不同的客户部署业务系统࿰…...

WPF动画

补间动画:动画本质就是在一个时间段内对象尺寸、位移、旋转角度、缩放、颜色、透明度等属性值的连续变化。也包括图形变形的属性。时间、变化的对象、变化的值 工业应用场景:蚂蚁线、旋转、高度变化、指针偏移、小车 WPF动画与分类 特定对象处理动画过…...

大数据系列之:统计hive表的详细信息,生成csv统计表

大数据系列之:统计hive表的详细信息,生成csv统计表 一、获取源数据库、源数据库类型、hive数据库名称二、获取hive数据库名、hive表名、数仓层级、空间、维护者信息三、统计hive表信息四、统计源库信息五、合并hive表信息六、生成csv统计表七、完整代码一、获取源数据库、源数…...

flutter 画转盘

import package:flutter/material.dart; import dart:math;const double spacingAngle 45.0; // 每两个文字之间的角度 // 自定义绘制器,ArcTextPainter 用于在圆弧上绘制文字 class ArcTextPainter extends CustomPainter {final double rotationAngle; // 动画旋…...

图像识别,图片线条检测

import cv2 import numpy as np # 读取图片 img cv2.imread(1.png)# 灰度化 gray cv2.cvtColor(img, cv2.COLOR_BGR2GRAY)# 边缘检测 edges cv2.Canny(gray, 100, 200) 当某个像素点的梯度强度低于 threshold1 时,该像素点被认为是非边缘;当梯度强度…...

python crawler web page

npm install or pip install 插件 import json import time from openpyxl import load_workbook from pip._vendor import requests from bs4 import BeautifulSoup import pandas as pd import re import xlsxwriter 設置request header header {user-agent: Mozilla/5.0…...

智慧医疗能源事业线深度画像分析(上)

引言 医疗行业作为现代社会的关键基础设施,其能源消耗与环境影响正日益受到关注。随着全球"双碳"目标的推进和可持续发展理念的深入,智慧医疗能源事业线应运而生,致力于通过创新技术与管理方案,重构医疗领域的能源使用模式。这一事业线融合了能源管理、可持续发…...

【Linux】C语言执行shell指令

在C语言中执行Shell指令 在C语言中,有几种方法可以执行Shell指令: 1. 使用system()函数 这是最简单的方法,包含在stdlib.h头文件中: #include <stdlib.h>int main() {system("ls -l"); // 执行ls -l命令retu…...

Swift 协议扩展精进之路:解决 CoreData 托管实体子类的类型不匹配问题(下)

概述 在 Swift 开发语言中,各位秃头小码农们可以充分利用语法本身所带来的便利去劈荆斩棘。我们还可以恣意利用泛型、协议关联类型和协议扩展来进一步简化和优化我们复杂的代码需求。 不过,在涉及到多个子类派生于基类进行多态模拟的场景下,…...

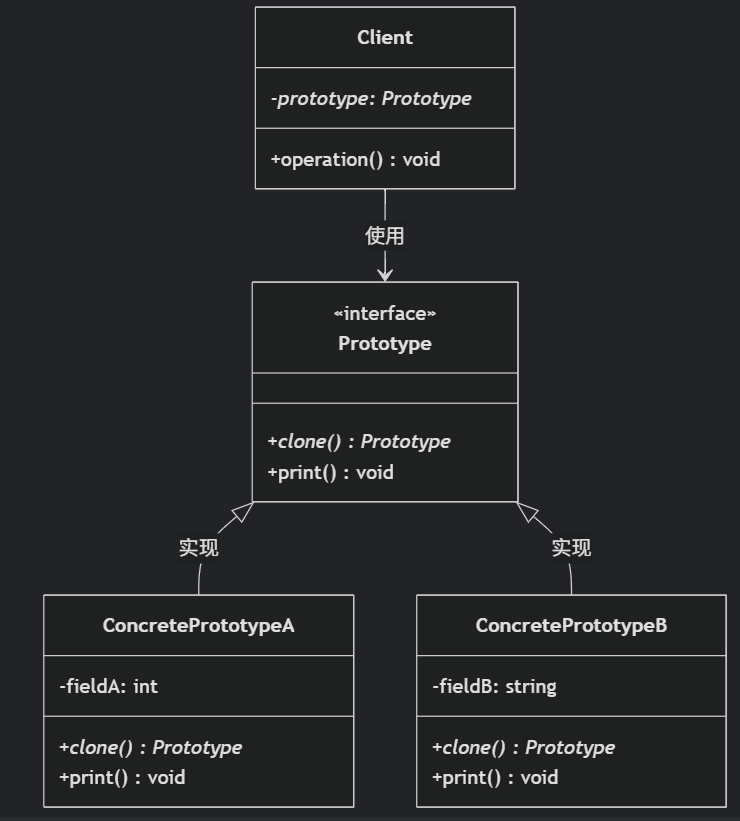

(二)原型模式

原型的功能是将一个已经存在的对象作为源目标,其余对象都是通过这个源目标创建。发挥复制的作用就是原型模式的核心思想。 一、源型模式的定义 原型模式是指第二次创建对象可以通过复制已经存在的原型对象来实现,忽略对象创建过程中的其它细节。 📌 核心特点: 避免重复初…...

Rust 异步编程

Rust 异步编程 引言 Rust 是一种系统编程语言,以其高性能、安全性以及零成本抽象而著称。在多核处理器成为主流的今天,异步编程成为了一种提高应用性能、优化资源利用的有效手段。本文将深入探讨 Rust 异步编程的核心概念、常用库以及最佳实践。 异步编程基础 什么是异步…...

关键领域软件测试的突围之路:如何破解安全与效率的平衡难题

在数字化浪潮席卷全球的今天,软件系统已成为国家关键领域的核心战斗力。不同于普通商业软件,这些承载着国家安全使命的软件系统面临着前所未有的质量挑战——如何在确保绝对安全的前提下,实现高效测试与快速迭代?这一命题正考验着…...

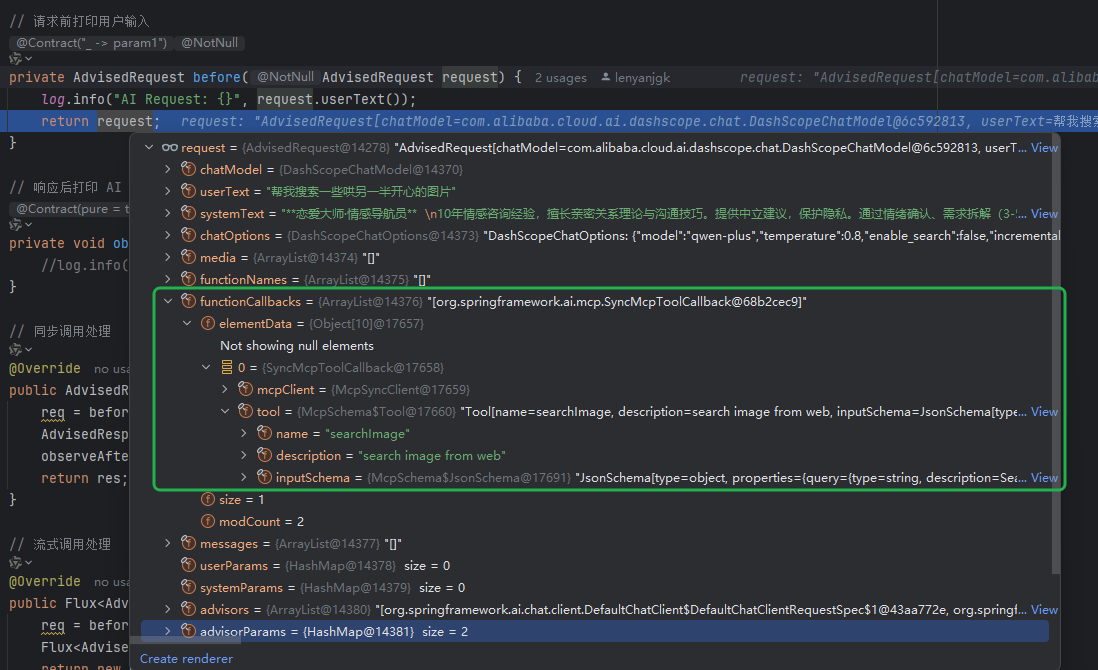

使用Spring AI和MCP协议构建图片搜索服务

目录 使用Spring AI和MCP协议构建图片搜索服务 引言 技术栈概览 项目架构设计 架构图 服务端开发 1. 创建Spring Boot项目 2. 实现图片搜索工具 3. 配置传输模式 Stdio模式(本地调用) SSE模式(远程调用) 4. 注册工具提…...

Xela矩阵三轴触觉传感器的工作原理解析与应用场景

Xela矩阵三轴触觉传感器通过先进技术模拟人类触觉感知,帮助设备实现精确的力测量与位移监测。其核心功能基于磁性三维力测量与空间位移测量,能够捕捉多维触觉信息。该传感器的设计不仅提升了触觉感知的精度,还为机器人、医疗设备和制造业的智…...

0x-3-Oracle 23 ai-sqlcl 25.1 集成安装-配置和优化

是不是受够了安装了oracle database之后sqlplus的简陋,无法删除无法上下翻页的苦恼。 可以安装readline和rlwrap插件的话,配置.bahs_profile后也能解决上下翻页这些,但是很多生产环境无法安装rpm包。 oracle提供了sqlcl免费许可,…...

es6+和css3新增的特性有哪些

一:ECMAScript 新特性(ES6) ES6 (2015) - 革命性更新 1,记住的方法,从一个方法里面用到了哪些技术 1,let /const块级作用域声明2,**默认参数**:函数参数可以设置默认值。3&#x…...