SPI(Serial Peripheral Interface)串行外围设备接口

SPI概述:

SPI协议最初由Motorola公司(现为NXP Semiconductors的一部分)在20世纪80年代中期开发。最初是为了在其68000系列微控制器中实现高速、高效的串行通信。该协议旨在简化微控制器与外围设备之间的数据传输。

-

1980年代:SPI协议迅速被其他半导体制造商采纳,并逐渐成为嵌入式系统中的事实标准。尽管SPI从未被任何正式的标准组织或行业标准小组正式标准化,但它在实际应用中被广泛接受。

-

1990年代初:SPI协议被JEDEC(电子设备工程联合委员会)标准化,这进一步推动了其在电子行业中的广泛应用。

SPI(Serial Peripheral Interface,串行外围设备接口)是一种高速的、全双工、同步的通信总线,用于短距离通信,主要应用在嵌入式系统中。

-

高速:SPI的通信速率可以达到数兆比特每秒(Mbps),具体速率取决于硬件设计和应用场景。

-

全双工:SPI支持同时发送和接收数据,这意味着主设备和从设备可以在同一时间进行数据交换。

-

同步串行通信:SPI使用时钟信号来同步数据的传输。数据在时钟信号的控制下逐位传输,确保数据的准确性和同步性。

SPI信号线

SPI协议通常使用四根线(SCLK、MOSI、MISO、SS)。

-

SCLK(时钟线):由主设备提供时钟信号,用于同步数据传输。

-

MOSI(主设备数据输出,从设备数据输入):主设备向从设备发送数据。

-

MISO(主设备数据输入,从设备数据输出):从设备向主设备发送数据。

-

CS/SS(片选线):用于选择特定的从设备。一个主设备可以通过多条CS线连接多个从设备。

SCLK(Serial Clock)

MOSI(Master Out Slave In)

MISO(Master In Slave Out)

CS/SS(Chip Select / Slave Select)

SPI协议也可以根据需要简化为三根线。

-

半双工模式:合并MOSI/MISO为单一数据线(SDIO),通过方向控制切换传输方向。

SPI时序

SPI协议定义了四种工作模式(Mode 0、Mode 1、Mode 2、Mode 3),这些模式主要区别在于时钟信号的极性(CPOL/POL)和相位(CPHA/PHA)。

-

(POL=1, PHA=1):时钟空闲状态为高电平,数据在第一个时钟下降沿之后采样。

-

(POL=1, PHA=0):时钟空闲状态为高电平,数据在第一个时钟上升沿之后采样。

-

(POL=0, PHA=1):时钟空闲状态为低电平,数据在第一个时钟上升沿之后采样。

-

(POL=0, PHA=0):时钟空闲状态为低电平,数据在第一个时钟下降沿之后采样。

i.MX6ull SPI介绍

The Enhanced Configurable Serial Peripheral Interface (ECSPI) is a full-duplex,synchronous, four-wire serial communication block.The ECSPI contains a 64 x 32 receive buffer (RXFIFO) and a 64 x 32 transmit buffer(TXFIFO). With data FIFOs, the ECSPI allows rapid data communication with fewersoftware interrupts. The figure below shows a block diagram of the ECSPI.增强型可配置串行外设接口(Enhanced Configurable Serial Peripheral Interface,简称ECSPI)是一个全双工、同步、四线串行通信模块。ECSPI包含一个64x32的接收缓冲器(RXFIFO)和一个64x32的发送缓冲器(TXFIFO)。通过数据FIFO,ECSPI允许快速数据通信,减少软件中断。

ECSPI结构框图

ECSPI 关键特性

• Full-duplex synchronous serial interface全双工同步串行接口• Master/Slave configurable主/从可配置• Four Chip Select (SS) signals to support multiple peripherals四个片选(SS)信号以支持多个外设• Transfer continuation function allows unlimited length data transfers传输继续功能允许不限长度的数据传输• 32-bit wide by 64-entry FIFO for both transmit and receive data32位宽、64项的发送和接收数据FIFO(先进先出缓冲区)• Polarity and phase of the Chip Select (SS) and SPI Clock (SCLK) are configurable片选(SS)和SPI时钟(SCLK)的极性和相位可配置• Direct Memory Access (DMA) support直接内存访问(DMA)支持• Max operation frequency up to the reference clock frequency.最高操作频率可达参考时钟频率

ECSPI 时钟

ECSPI 模式

ECSPI支持三种模式:(Master Mode 主机模式),(Slave Mode 从机模式),(Low Power Modes 低功耗模式)

本文只介绍i.MX6ull开发板ECSPI的Master Mode 主机模式,Slave Mode 从机模式和Low Power Modes 低功耗模式可参考i.MX6ull开发板的数据手册

Master Mode 主机模式

When the ECSPI is configured as a master, it uses a serial link to transfer data between the ECSPI and an external slave device.当ECSPI(增强型可配置串行外设接口)被配置为主设备时,它使用串行链路在ECSPI和外部从设备之间传输数据。One of the Chip Select (SS) signals and the clock signal (SCLK) are used to transfer data between two devices. If the external device is a transmit-only device, the ECSPI master's output port can be ignored and used for other purposes. In order to use the internal TXFIFO and RXFIFO, two auxiliary output signals, Chip Select (SS) and SPI_RDY, are used for data transfer rate control. Software can also configure the sample period control register to a fixed data transfer rate.片选(SS)信号之一和时钟信号(SCLK)被用来在两个设备之间传输数据。如果外部设备仅为发送设备,可以忽略ECSPI主设备的输出端口,并将其用于其他目的。为了使用内部的发送FIFO(TXFIFO)和接收FIFO(RXFIFO),两个辅助输出信号,片选(SS)和SPI_RDY,被用于数据传输速率控制。软件也可以配置采样周期控制寄存器以设定一个固定的数据传输速率。When the ECSPI is in Master mode the SS, SCLK, and MOSI are output signals, and the MISO signal is an input当ECSPI处于主模式时,SS、SCLK和MOSI是输出信号,而MISO是输入信号。The Chip Select (SS) signal enables the selected external SPI device, and the SCLK synchronizes the data transfer.片选(SS)信号用于启用选定的外部SPI设备,而SCLK(时钟)信号则同步数据传输。

Master Mode with SPI_RDY

SPI_RDY信号是一个辅助控制信号,它在SPI通信中用于流量控制和数据传输同步。在某些情况下,SPI_RDY信号可以指示从机是否准备好接收数据,或者帮助主设备控制数据的发送节奏,避免从设备因过载而无法处理过多的数据。在数据传输速率较高的应用中,RDY允许主设备控制数据的发送节奏。如果多个设备连接到同一个SPI总线上,RDY信号可以帮助主设备分批次向各设备发送数据,提高了系统效率。

在ECSPI(增强型可配置串行外设接口)中,DRCTL位用于设置SPI_RDY信号,为0的话不关心SPI_RDY信号;为1的话SPI_RDY信号为边沿触发;为2的话SPI_DRY是电平触发。如果SPI Data Ready Control (ECSPI_CONREG[DRCTL])位包含01或10,SPI_RDY信号控制SPI突发的开始。如果ECSPI_CONREG[DRCTL]被设置为01,则只有在检测到SPI_RDY信号的下降沿时,SPI突发才能被触发。如果SPI Data Ready Control (ECSPI_CONREG[DRCTL])被设置为10,则只有在SPI_RDY信号为低时,SPI突发才能被触发。

SPI突发传输

一种在SPI通信协议下进行数据传输的方式,它允许在单个传输事务中连续传输多个数据字,从而提高数据传输效率。在这种模式下,主设备首先发送一个选择信号,然后可以连续发送多个数据字节,而从设备则可以在不发送响应信号的情况下接收这些数据字节。在传输完成后,主设备发送一个停止信号,以结束通信。

Master Mode with SS_CTL[3:0] Control

SS_CTL[3:0]决定了当前操作是单次突发还是多次突发。当SPI片选波形选择SS_CTL[3:0]被设置时,当前操作是多次突发传输。当SPI片选波形选择SS_CTL[3:0]位被清除时,当前操作是单次突发传输。一个SPI突发可以包含多个字,如ECSPI_CONREG寄存器中BURST LENGTH字段所定义。

Master Mode with Phase Control

The Phase Control (ECSPI_CONREG[PHA]) bit controls how the transmit data shifts out and the receive data shifts in.相位控制(ECSPI_CONREG[PHA])位决定了传输数据的移出方式和接收数据的移入方式。When the Phase control (ECSPI_CONREG[PHA]) bit is set, the transmit data will shift out on the rising edge of SCLK, and the receive data is latched on the falling edge of SCLK. The most-significant bit is output on the first rising SCLK edge. When ECSPI_CONREG[PHA] is cleared, the transmit data is shifted out on the falling edge of SCLK and the receive data is latched on the rising edge of SCLK. The MSB is output when the host processor loads the transmitted data.当相位控制(ECSPI_CONREG[PHA])位被设置时,传输数据将在SCLK(时钟)的上升沿移出,接收数据在SCLK的下降沿被锁存。最高有效位(MSB)在第一个SCLK上升沿被输出。

当ECSPI_CONREG[PHA]被清除时,传输数据在SCLK的下降沿移出,接收数据在SCLK的上升沿被锁存。MSB在主处理器加载要传输的数据时输出。

Inverting the SCLK polarity does not impact the edge-triggered operations because they are internal to the serial peripheral interface master.反转SCLK极性不会影响边沿触发操作,因为这些操作是串行外设接口主设备内部的。

ECSPI Reset

Whenever a device reset occurs, a reset is performed on the ECSPI, resetting all registers to their default values.Software can reset the block using the CONREG[EN] bit;每当发生设备复位时,ECSPI(增强型可配置串行外设接口)也会执行复位操作,将其所有寄存器重置为默认值。

软件可以通过设置CONREG寄存器中的[EN]位来复位ECSPI模块。

ECSPI Initialization

This section provides initialization information for ECSPI.To initialize the block:1. Clear the EN bit in ECSPI_CONREG to reset the block.复位模块:清除ECSPI_CONREG(ECSPI控制寄存器)中的EN位以复位该模块2. Enable the clocks for ECSPI within the CCM.使能时钟:在CCM(时钟控制模块)内为ECSPI使能时钟。

3. Configure the Control Register and then set the EN bit in the ECSPI_CONREG toput ECSPI out of reset.配置控制寄存器并退出复位:配置控制寄存器,然后在ECSPI_CONREG中设置EN位,使ECSPI退出复位状态。

4. Configure corresponding IOMUX for ECSPI external signals.配置IOMUX:为ECSPI的外部信号配置相应的IOMUX(输入/输出多路复用器)。

5. Configure registers of ECSPI properly according to the specifications of the external SPI device.正确配置ECSPI寄存器:根据外部SPI设备的技术规格,正确配置ECSPI的寄存器。

ECSPI重点寄存器

Receive Data Register (ECSPIx_RXDATA)

The Receive Data register (ECSPI_RXDATA) is a read-only register that forms the topword of the 64 x 32 receive FIFO. This register holds the data received from an external SPI device during a data transaction. Only word-sized read operations are allowed.接收数据寄存器(ECSPI_RXDATA)是一个只读寄存器,它构成了64x32接收FIFO(先进先出缓冲区)的顶部字。该寄存器保存了在数据事务期间从外部SPI设备接收到的数据。只允许进行字大小的读取操作。

Transmit Data Register (ECSPIx_TXDATA)

The Transmit Data (ECSPI_TXDATA) register is a write-only data register that formsthe bottom word of the 64 x 32 TXFIFO. The TXFIFO can be written to as long as it isnot full, even when the SPI Exchange bit (XCH) in ECSPI_CONREG is set. This allowssoftware to write to the TXFIFO during a SPI data exchange process. Writes to thisregister are ignored when the ECSPI is disabled (ECSPI_CONREG[EN] bit is cleared).发送数据(ECSPI_TXDATA)寄存器是一个只写的数据寄存器,它构成了64x32发送FIFO(先进先出缓冲区)的底部字。只要发送FIFO未满,就可以对其进行写入操作,即使在ECSPI_CONREG中的SPI数据交换位(XCH)被设置的情况下也是如此。这允许软件在SPI数据交换过程中向发送FIFO写入数据。当ECSPI被禁用(ECSPI_CONREG[EN]位被清除)时,对该寄存器的写入操作将被忽略。

Config Register (ECSPIx_CONFIGREG)

The Config Register (ECSPI_CONFIGREG) allows software to configure each SPIchannel, configure its operating modes, specify the phase and polarity of the clock,configure the Chip Select (SS), and define the HT transfer length. Note, HT mode is not supported by this product.配置寄存器(ECSPI_CONFIGREG)允许软件配置每个SPI通道,设置其工作模式,指定时钟的相位和极性,配置芯片选择(SS),以及定义HT(高吞吐量)传输长度。请注意,本产品不支持HT模式。

SCLK_CTL(23-20位):控制每个SPI通道的SCLK(时钟)非活动状态

- 0表示保持低电平。

- 1表示保持高电平。

DATA_CTL(19-16位):控制每个SPI通道数据线的非活动状态

- 0表示保持高电平。

- 1表示保持低电平。

SS_POL(15-12位):SPI SS(片选)极性选择

在主模式和从模式下,此字段选择Chip Select (SS)信号的极性。

- 0表示保持低电平。

- 1表示保持高电平。

SS_CTL(11-8位):SPI SS波形选择

在主模式下,当SMC(开始模式控制)位被清除时,此字段控制Chip Select (SS)信号的输出波形。如果设置了SMC位,则忽略SS_CTL。

在从模式下,此位控制SPI突发完成的时机。

- 0表示主模式下只传输一个SPI突发。

- 1表示主模式下在SPI突发之间否定Chip Select (SS)信号,传输多个SPI突发。

SCLK_POL(7-4位):SPI时钟极性控制

- 0表示活动高极性(0=空闲)。

- 1表示活动低极性(1=空闲)。

SCLK_PHA(7-4位):SPI时钟/数据相位控制

- 0表示相位0操作。

- 1表示相位1操作。

Control Register (ECSPIx_CONREG)

The Control Register (ECSPI_CONREG) allows software to enable the ECSPI ,

configure its operating modes, specify the divider value, and SPI_RDY control signal,

and define the transfer length.控制寄存器(ECSPI_CONREG)允许软件启用ECSPI(增强型串行外设接口),配置其工作模式,指定分频值和SPI_RDY控制信号,并定义传输长度。

BURST_LENGTH(31-20位):定义了要传输的SPI突发的长度

在主模式下,它控制每个SPI突发的位数。由于移位寄存器总是从传输FIFO加载32位数据,因此只有n个最低有效位(n = BURST_LENGTH + 1)将被移出,其余位将被忽略。最大可以传输2^12位。

CHANNEL_SELECT(19-18位):SPI通道选择位

在主模式下,通过断言Chip Select (SSn) 输出来选择外部从设备。一次只能激活选定的Chip Select (SSn) 信号;其余三个信号将被否定。

DRCTL(17-16位):SPI数据就绪控制

此字段选择在主模式下使用SPI_RDY信号。ECSPI在开始SPI突发之前会检查此字段。

- 10:突发将由SPI_RDY信号的低电平触发(电平触发)。

- 01:突发将由SPI_RDY信号的下降沿触发(边沿触发)。

- 00:SPI_RDY信号不关心。

PRE_DIVIDER(15-12位):SPI预分频器

ECSPI使用两级分频器生成SPI时钟。

POST_DIVIDER(11-8位):SPI后分频器

ECSPI使用两级分频器生成SPI时钟。

CHANNEL_MODE(7-4位):用于为每个SPI通道选择模式

- CHANNEL_MODE[3]:对应SPI通道3。

- CHANNEL_MODE[2]:对应SPI通道2。

- CHANNEL_MODE[1]:对应SPI通道1。

- CHANNEL_MODE[0]:对应SPI通道0。

- 0:从模式(Slave mode)。

- 1:主模式(Master mode)。

SMC:开始模式控制位

仅适用于配置为主模式的通道(CHANNEL_MODE=1)。控制ECSPI如何启动SPI突发,可以通过SPI交换位或立即在TXFIFO写入时启动。

- 0:SPI交换位(XCH)控制何时可以启动SPI突发。设置XCH位将启动一个或多个SPI突发,由SPI SS波形选择(SS_CTL)控制。

- 1:当数据写入TXFIFO时立即启动SPI突发。

XCH:SPI交换位

仅适用于配置为主模式的通道(CHANNEL_MODE=1)。如果开始模式控制(SMC)位被清除,向此位写入1将根据SPI SS波形选择(SS_CTL)启动一个或多个SPI突发。XCH位在数据交换进行中或ECSPI等待活动输入(如果通过DRCTL启用了SPIRDY)时保持设置。当TXFIFO和移位寄存器中的所有数据都被移出后,此位会自动清除。

0:空闲。

1:启动交换(写入)或忙(读取)。

EN(0位):SPI使能控制位

此位启用ECSPI。在写入其他寄存器或启动交换之前,必须设置此位。向此位写入零将禁用块并重置内部逻辑,ECSPI_CONREG除外。模块被禁用时,其内部时钟将被关闭。

- 0:禁用。

- 1:启用。

Status Register (ECSPIx_STATREG)

The ECSPI Status Register (ECSPI_STATREG) reflects the status of the ECSPI'soperating condition. If the ECSPI is disabled, this register reads 0x0000_0003.ECSPI状态寄存器(ECSPI_STATREG)反映了ECSPI(增强型可配置串行外设接口)的运行状态。 如果ECSPI被禁用,该寄存器的读数为0x0000_0003。

TC:传输完成状态位

写入1可以清除。

- 0:传输正在进行中。

- 1:传输已完成。

RO:RXFIFO溢出位

当该位被设置时,表示RXFIFO已溢出。写入1可以清除。

- 0:RXFIFO没有溢出。

- 1:RXFIFO已溢出。

RF:RXFIFO满位

当RXFIFO满时,该位被设置。

- 0:未满。

- 1:已满。

RDR:RXFIFO数据请求位

1.当RXTDE被清除时:

- 0:RXFIFO中的数据条目数不大于RX_THRESHOLD。

- 1:RXFIFO中的数据条目数大于RX_THRESHOLD。

2.当RXTDE被设置时:

- 0:RXFIFO中的数据条目数不大于RX_THRESHOLD。

- 1:RXFIFO中的数据条目数大于RX_THRESHOLD或存在DMA TAIL DMA条件。

RR:RXFIFO就绪位

当RXFIFO中存储了一个或多个字时,该位被设置。

- 0:RXFIFO中没有有效数据。

- 1:RXFIFO中有多个字。

TF:TXFIFO满位

当TXFIFO满时,该位被设置。

TDR:TXFIFO数据请求位。

- 1:TXFIFO中的有效数据槽数不大于TX_THRESHOLD。

- 0:TXFIFO中的有效数据槽数大于TX_THRESHOLD。

TE:TXFIFO空位

如果TXFIFO为空,该位被设置。

- 1:TXFIFO为空。

- 0:TXFIFO包含一个或多个字。

Test Control Register (ECSPIx_TESTREG)

The Test Control Register (ECSPI_TESTREG) provides software a mechanism tointernally connect the receive and transmit devices of the ECSPI, and monitor thecontents of the receive and transmit FIFOs.测试控制寄存器(ECSPI_TESTREG)为软件提供了一种机制,可以内部连接ECSPI的接收和发送设备,并监控接收和发送FIFO的内容。这使得开发者能够在调试过程中检查数据流,确保数据正确地在发送和接收设备之间传输,同时也可以用来测试ECSPI接口的功能是否正常工作。

LBC(31位):回环控制位。

此位仅在主模式下使用。当设置此位时,ECSPI内部连接发送器和接收器部分,移位寄存器中最高位的数据被回环到移位寄存器的最低位。这样,可以对完整的发送/接收路径进行自检。输出引脚不受影响,输入引脚被忽略。

- 0:未连接。

- 1:发送器和接收器部分内部连接以进行回环。

RXCNT(14-8位):RXFIFO计数器。指示RXFIFO中的字数。

TXCNT(6-0位):TXFIFO计数器。指示TXFIFO中的字数。

示例代码:

下面代码只是对i.MX6ull开发板中ECSPI模块的基础应用

#include "spi.h"//管脚初始化

void spi_gpio_init()

{/*IOMUXC_SW_MUX_CTL_PAD_UART2_TX_DATAGPIO1_IO20 ECSPI3_SS01000 ALT8 — Select mux mode: ALT8 mux port: ECSPI3_SS0 of instance: ecspi3*/IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO20 &= ~(0xf<<0);IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO20 |= (0x8<<0);/*IOMUXC_SW_MUX_CTL_PAD_UART2_RX_DATAGPIO1_IO21 ECSPI3_SCLK1000 ALT8 — Select mux mode: ALT8 mux port: ECSPI3_SCLK of instance: ecspi3*/IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO21 &= ~(0xf<<0);IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO21 |= (0x8<<0);/*IOMUXC_SW_MUX_CTL_PAD_UART2_CTS_BGPIO1_IO22 ECSPI3_MOSI1000 ALT8 — Select mux mode: ALT8 mux port: ECSPI3_MOSI of instance: ecspi3*/IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO22 &= ~(0xf<<0);IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO22 |= (0x8<<0);/*IOMUXC_SW_MUX_CTL_PAD_UART2_RTS_BGPIO1_IO23 ECSPI3_MISO1000 ALT8 — Select mux mode: ALT8 mux port: ECSPI3_MISO of instance: ecspi3*/IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO23 &= ~(0xf<<0);IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO23 |= (0x8<<0);

}//SPI控制器初始化

/*

控制寄存器(ECSPI_CONREG)

允许软件启用ECSPI(增强型串行外设接口)

配置其工作模式 operating modes

指定分频值divider value和SPI_RDY控制信号

定义传输长度。

*/

void spi_control_init()

{//将控制寄存器位清零ECSPI3->CONREG = 0;/* 定义SPI突发的长度[31–20] BURST_LENGTH0x07 A SPI burst contains the 8 LSB in a word.*/ECSPI3->CONREG |= (0X07<<20);/*SPI数据准备控制,ECSPI在开始SPI突发前会检查此字段。[17–16] DRCTL00 The SPI_RDY signal is a don't care.*//*SPI预分频器[15–12] PRE_DIVIDER*/ECSPI3->CONREG |= (0x9<<12);/*SPI后分频器[11–8] POST_DIVIDER*/ECSPI3->CONREG |= (0x1<<8);/*启动模式控制,控制ECSPI如何开始SPI突发[3] SMC1 Immediately starts a SPI burst when data is written in TXFIFO.*/ECSPI3->CONREG |= (0x1<<3);/*SPI块使能控制[0] EN0 Disable the block.1 Enable the block*/ECSPI3->CONREG |= (0x1<<0);

}//配置SPI通道

/*

配置寄存器(ECSPI_CONFIGREG)

允许软件配置每个SPI通道

设置其工作模式

指定时钟的相位和极性

配置芯片选择(SS)---*使用外部片选

定义HT(高吞吐量)传输长度。

请注意,本产品不支持HT模式。

*/

void spi_channel_config(uint_fast8_t channel,uint_fast8_t polarity,uint_fast8_t phase)

{/*用于选择四个外部SPI主/从设备中的一个进行通信通过断言相应的Chip Select (SSn) 输出来选择外部从设备SPI通信中,Chip Select信号用于通知从设备何时开始和结束数据传输。控制寄存器(ECSPI_CONREG)[19-18] CHANNEL_SELECTeg:00:选择通道0,此时Chip Select 0 (SS0) 将被断言。与SS0关联的从设备会被激活*/ECSPI3->CONREG |= (channel<<18);/*控制每个SPI通道的SCLK(时钟)信号在非活动状态下的电平。SCLK_CTL [23-20] SCLK CTL[3] is for SPI channel 3.SCLK CTL[2] is for SPI channel 2.SCLK CTL[1] is for SPI channel 1.SCLK CTL[0] is for SPI channel 0.0 Stay low.1 Stay high.*/ECSPI3->CONFIGREG &= ~(0xf<<20);ECSPI3->CONFIGREG |= (polarity<<(channel+20));/*控制每个SPI通道的数据线在非活动状态下的电平。DATA_CTL [19-16]0 Stay high.1 Stay low.*/ECSPI3->CONFIGREG &= ~(0xf<<16);ECSPI3->CONFIGREG |= (1<<(channel+16));/*选择每个SPI通道的Chip Select(CS)信号的极性。SS_POL [15-12]0 Active low.1 Active high.*/ECSPI3->CONFIGREG &= ~(0xf<<12);ECSPI3->CONFIGREG &= ~(1<<(channel+12));/*SPI通道选择模式控制寄存器(ECSPI_CONREG)[7–4] CHANNEL_MODE0 Slave mode.1 Master mode.*/ECSPI3->CONREG |= (1<<(channel+4));/*SCLK_POL (7-4) SPI时钟极性控制0 Active high polarity (0 = Idle).1 Active low polarity (1 = Idle).*/ECSPI3->CONFIGREG |= (polarity<<(channel+4));/*SCLK_PHA (3-0) SPI时钟/数据相位控制0 Phase 0 operation.1 Phase 1 operation.*/ECSPI3->CONFIGREG |= (phase<<(channel));

}/*

ECSPI状态寄存器(ECSPI_STATREG)

用于反映ECSPI(增强型串行外设接口)的运行状态

*/

//发送数据

uint_fast32_t spi_Transfer_data(uint_fast8_t data)

{uint_fast32_t resultdata;/*保存输入的数据Transmit Data Register (ECSPIx_TXDATA)数据由软件写入,以供SPI硬件在数据传输过程中发送。*/ECSPI3->TXDATA = data;/*判断数据是否传入TXFIFOTE [0]0 TXFIFO contains one or more words.1 TXFIFO is empty*/while(ECSPI3->STATREG & (0x1<<0)){}/*判断传输是否完成TC [7]Transfer Completed Status bit. Writing 1 to this bit clears it.0 Transfer in progress.1 Transfer completed.*/while(!(ECSPI3->STATREG & (0x1<<7))){}/*判断数据是否接收到数据[3] RR 指示接收FIFO(RXFIFO)中的数据状态0 No valid data in RXFIFO.1 More than 1 word in RXFIFO.*/while(!(ECSPI3->STATREG & (0x1<<3))){}/*保存接收到的的数据Receive Data Register (ECSPIx_RXDATA)用于存储在数据传输期间从外部SPI设备接收到的数据ECSPI_RXDATA寄存器的读取操作必须是字大小的*/resultdata = ECSPI3->RXDATA;return resultdata;

}//片选信号

void spi_cs_start()

{GPIO1->GDIR |= (0x1<<20);GPIO1->DR &= ~(0x1<<20);

}

void spi_cs_stop()

{GPIO1->DR |= (0x1<<20);

}void test_spi()

{spi_gpio_init();spi_control_init();spi_channel_config(1,0,1);uint_fast32_t tmpchar;for(tmpchar='A';tmpchar<='Z';tmpchar++){spi_cs_start();uint_fast8_t result = spi_Transfer_data(tmpchar);spi_cs_stop();uart_printf("char:%c\r\n",result);gpt_delay_seconds(1);}

}结语:

无论你是初学者还是有经验的开发者,我希望我的博客能对你的学习之路有所帮助。如果你觉得这篇文章有用,不妨点击收藏,或者留下你的评论分享你的见解和经验,也欢迎你对我博客的内容提出建议和问题。每一次的点赞、评论、分享和关注都是对我的最大支持,也是对我持续分享和创作的动力

相关文章:

SPI(Serial Peripheral Interface)串行外围设备接口

SPI概述: SPI协议最初由Motorola公司(现为NXP Semiconductors的一部分)在20世纪80年代中期开发。最初是为了在其68000系列微控制器中实现高速、高效的串行通信。该协议旨在简化微控制器与外围设备之间的数据传输。 1980年代:SPI协…...

Java 8 Stream API

通过 Stream.of 方法直接传入多个元素构成一个流 String[] arr {“a”, “b”, “c”}; Stream.of(arr).forEach(System.out::println); Stream.of(“a”, “b”, “c”).forEach(System.out::println); Stream.of(1, 2, “a”).map(item -> item.getClass().getName()…...

亚博microros小车-原生ubuntu支持系列:21 颜色追踪

背景知识 这个测试例子用到了很多opencv的函数,举个例子。 #cv2.findContours函数来找到二值图像中的轮廓。#参数:#参数1:输 入的二值图像。通常是经过阈值处理后的图像,例如在颜色过滤之后生成的掩码。#参数2(cv2.RETR_EXTERNA…...

GESP6级语法知识(六):(动态规划算法(六)多重背包)

多重背包(二维数组) #include <iostream> using namespace std; #define N 1005 int Asd[N][N]; //Asd[i][j]表示前 i 个物品,背包容量是 j 的情况下的最大价值。 int Value[N], Vol[N], S[N];int main() {int n, Volume;cin &g…...

MySQL 事务实现原理( 详解 )

MySQL 主要是通过: 锁、Redo Log、Undo Log、MVCC来实现事务 事务的隔离性利用锁机制实现 原子性、一致性和持久性由事务的 redo 日志和undo 日志来保证。 Redo Log(重做日志):记录事务对数据库的所有修改,在崩溃时恢复未提交的更改,保证事务…...

AI协助探索AI新构型自动化创新的技术实现

一、AI自进化架构的核心范式 1. 元代码生成与模块化重构 - 代码级自编程:基于神经架构搜索的强化学习框架,AI可通过生成元代码模板(框架的抽象层定义)自动组合功能模块。例如,使用注意力机制作为原子单元ÿ…...

九. Redis 持久化-RDB(详细讲解说明,一个配置一个说明分析,步步讲解到位)

九. Redis 持久化-RDB(详细讲解说明,一个配置一个说明分析,步步讲解到位) 文章目录 九. Redis 持久化-RDB(详细讲解说明,一个配置一个说明分析,步步讲解到位)1. RDB 概述2. RDB 持久化执行流程3. RDB 的详细配置4. RDB 备份&恢…...

mac连接linux服务器

1、mac连接linux服务器 # ssh -p 22 root192.168.1.152、mac指定密码连接linux服务器 (1) 先安装sshpass,下载后解压执行 ./configure && make && makeinstall https://sourceforge.net/projects/sshpass/ (2) 连接linux # sshpass -p \/\\\[\!\\wen12\$ s…...

oracle: 表分区>>范围分区,列表分区,散列分区/哈希分区,间隔分区,参考分区,组合分区,子分区/复合分区/组合分区

分区表 是将一个逻辑上的大表按照特定的规则划分为多个物理上的子表,这些子表称为分区。 分区可以基于不同的维度,如时间、数值范围、字符串值等,将数据分散存储在不同的分区 中,以提高数据管理的效率和查询性能,同时…...

使用Pygame制作“走迷宫”游戏

1. 前言 迷宫游戏是最经典的 2D 游戏类型之一:在一个由墙壁和通道构成的地图里,玩家需要绕过障碍、寻找通路,最终抵达出口。它不但简单易实现,又兼具可玩性,还能在此基础上添加怪物、道具、机关等元素。本篇文章将展示…...

AJAX案例——图片上传个人信息操作

黑马程序员视频地址: AJAX-Day02-11.图片上传https://www.bilibili.com/video/BV1MN411y7pw?vd_source0a2d366696f87e241adc64419bf12cab&spm_id_from333.788.videopod.episodes&p26 图片上传 <!-- 文件选择元素 --><input type"file"…...

Day35-【13003】短文,什么是双端队列?栈和队列的互相模拟,以及解决队列模拟栈时出栈时间开销大的方法

文章目录 第三节进一步讨论栈和队列双端队列栈和队列的相互模拟使用栈来模拟队列类型定义入队出队判空,判满 使用队列来模拟栈类型定义初始化清空操作判空,判满栈长度输出入栈出栈避免出栈时间开销大的方法 第三节进一步讨论栈和队列 双端队列 假设你芷…...

力扣 55. 跳跃游戏

🔗 https://leetcode.cn/problems/jump-game 题目 给一个数组 nums,最开始在 index 0,每次可以跳跃的区间是 0-nums[i]判断是否可以跳到数组末尾 思路 题解是用贪心,实际上模拟也可以过遍历可以到达的下标,判断其可…...

深入剖析 HTML5 新特性:语义化标签和表单控件完全指南

系列文章目录 01-从零开始学 HTML:构建网页的基本框架与技巧 02-HTML常见文本标签解析:从基础到进阶的全面指南 03-HTML从入门到精通:链接与图像标签全解析 04-HTML 列表标签全解析:无序与有序列表的深度应用 05-HTML表格标签全面…...

本地快速部署DeepSeek-R1模型——2025新年贺岁

一晃年初六了,春节长假余额马上归零了。今天下午在我的电脑上成功部署了DeepSeek-R1模型,抽个时间和大家简单分享一下过程: 概述 DeepSeek模型 是一家由中国知名量化私募巨头幻方量化创立的人工智能公司,致力于开发高效、高性能…...

MVC 文件夹:架构之美与实际应用

MVC 文件夹:架构之美与实际应用 引言 MVC(Model-View-Controller)是一种设计模式,它将应用程序分为三个核心组件:模型(Model)、视图(View)和控制器(Controller)。这种架构模式不仅提高了代码的可维护性和可扩展性,而且使得开发流程更加清晰。本文将深入探讨MVC文…...

Redis --- 秒杀优化方案(阻塞队列+基于Stream流的消息队列)

下面是我们的秒杀流程: 对于正常的秒杀处理,我们需要多次查询数据库,会给数据库造成相当大的压力,这个时候我们需要加入缓存,进而缓解数据库压力。 在上面的图示中,我们可以将一条流水线的任务拆成两条流水…...

如何确认设备文件 /dev/fb0 对应的帧缓冲设备是开发板上的LCD屏?如何查看LCD屏的属性信息?

要判断 /dev/fb0 是否对应的是 LCD 屏幕,可以通过以下几种方法: 方法 1:使用 fbset 命令查看帧缓冲设备的属性信息 Linux 的 帧缓冲设备(Framebuffer) 通常在 /dev/fbX 下,/dev/fb0 一般是主屏幕ÿ…...

C++多线程编程——基于策略模式、单例模式和简单工厂模式的可扩展智能析构线程

1. thread对象的析构问题 在 C 多线程标准库中,创建 thread 对象后,必须在对象析构前决定是 detach 还是 join。若在 thread 对象销毁时仍未做出决策,程序将会终止。 然而,在创建 thread 对象后、调用 join 前的代码中ÿ…...

AI与SEO关键词的完美结合如何提升网站流量与排名策略

内容概要 在当今数字营销环境中,内容的成功不仅依赖于高质量的创作,还包括高效的关键词策略。AI与SEO关键词的结合,正是这一趋势的重要体现。 AI技术在SEO中的重要性 在数字营销领域,AI技术的引入为SEO策略带来了前所未有的变革。…...

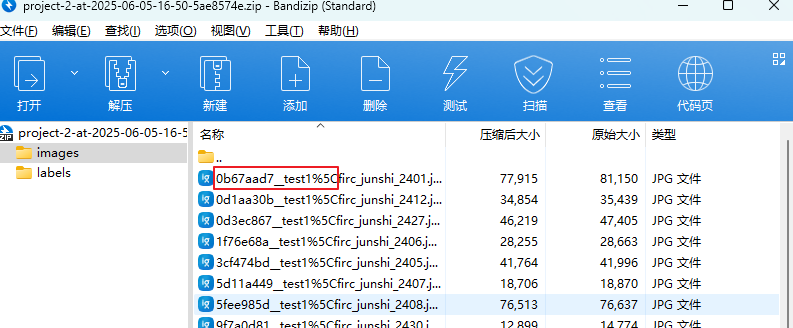

label-studio的使用教程(导入本地路径)

文章目录 1. 准备环境2. 脚本启动2.1 Windows2.2 Linux 3. 安装label-studio机器学习后端3.1 pip安装(推荐)3.2 GitHub仓库安装 4. 后端配置4.1 yolo环境4.2 引入后端模型4.3 修改脚本4.4 启动后端 5. 标注工程5.1 创建工程5.2 配置图片路径5.3 配置工程类型标签5.4 配置模型5.…...

工程地质软件市场:发展现状、趋势与策略建议

一、引言 在工程建设领域,准确把握地质条件是确保项目顺利推进和安全运营的关键。工程地质软件作为处理、分析、模拟和展示工程地质数据的重要工具,正发挥着日益重要的作用。它凭借强大的数据处理能力、三维建模功能、空间分析工具和可视化展示手段&…...

)

Java入门学习详细版(一)

大家好,Java 学习是一个系统学习的过程,核心原则就是“理论 实践 坚持”,并且需循序渐进,不可过于着急,本篇文章推出的这份详细入门学习资料将带大家从零基础开始,逐步掌握 Java 的核心概念和编程技能。 …...

智能仓储的未来:自动化、AI与数据分析如何重塑物流中心

当仓库学会“思考”,物流的终极形态正在诞生 想象这样的场景: 凌晨3点,某物流中心灯火通明却空无一人。AGV机器人集群根据实时订单动态规划路径;AI视觉系统在0.1秒内扫描包裹信息;数字孪生平台正模拟次日峰值流量压力…...

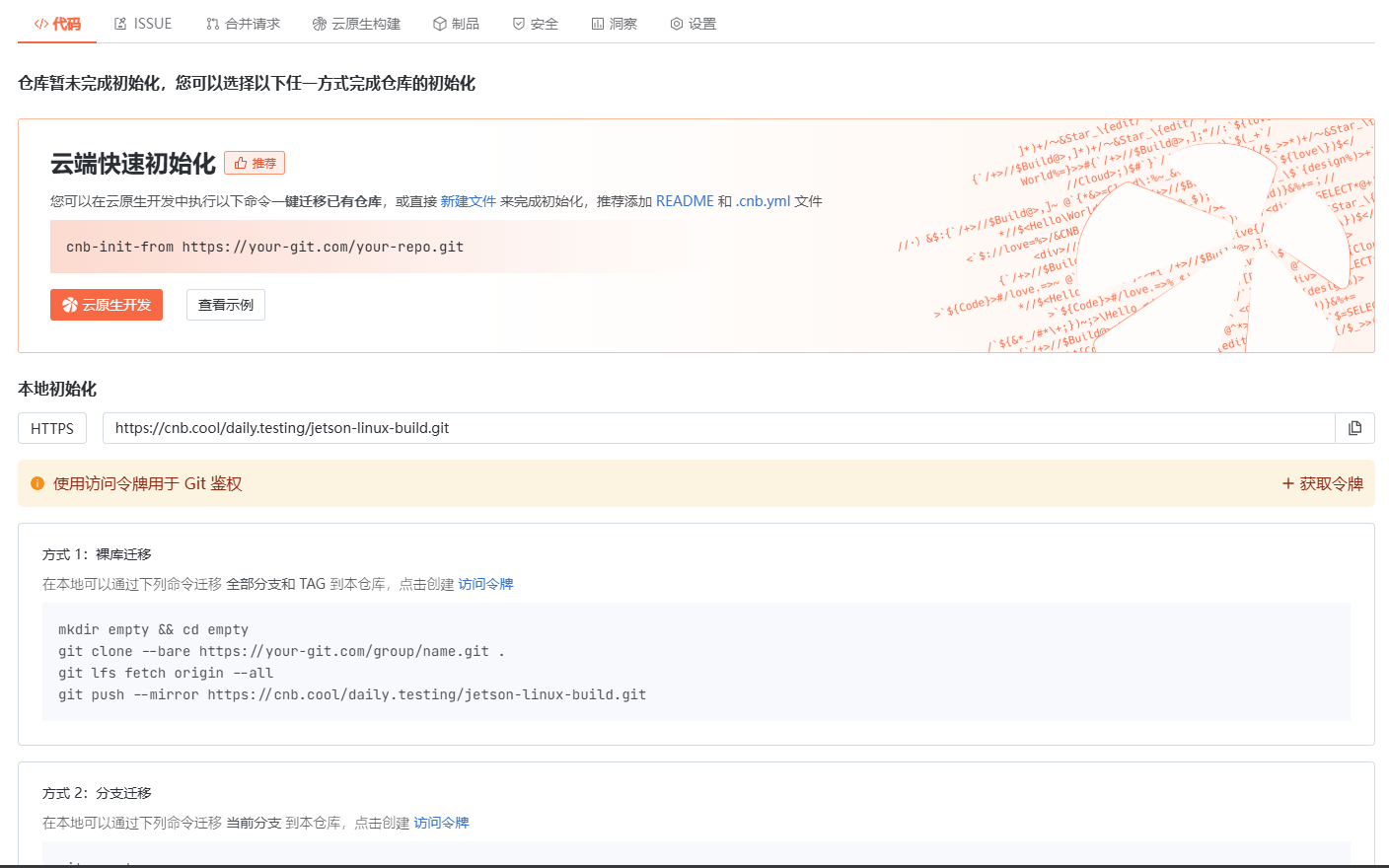

云原生玩法三问:构建自定义开发环境

云原生玩法三问:构建自定义开发环境 引言 临时运维一个古董项目,无文档,无环境,无交接人,俗称三无。 运行设备的环境老,本地环境版本高,ssh不过去。正好最近对 腾讯出品的云原生 cnb 感兴趣&…...

提供了哪些便利?)

现有的 Redis 分布式锁库(如 Redisson)提供了哪些便利?

现有的 Redis 分布式锁库(如 Redisson)相比于开发者自己基于 Redis 命令(如 SETNX, EXPIRE, DEL)手动实现分布式锁,提供了巨大的便利性和健壮性。主要体现在以下几个方面: 原子性保证 (Atomicity)ÿ…...

Mysql8 忘记密码重置,以及问题解决

1.使用免密登录 找到配置MySQL文件,我的文件路径是/etc/mysql/my.cnf,有的人的是/etc/mysql/mysql.cnf 在里最后加入 skip-grant-tables重启MySQL服务 service mysql restartShutting down MySQL… SUCCESS! Starting MySQL… SUCCESS! 重启成功 2.登…...

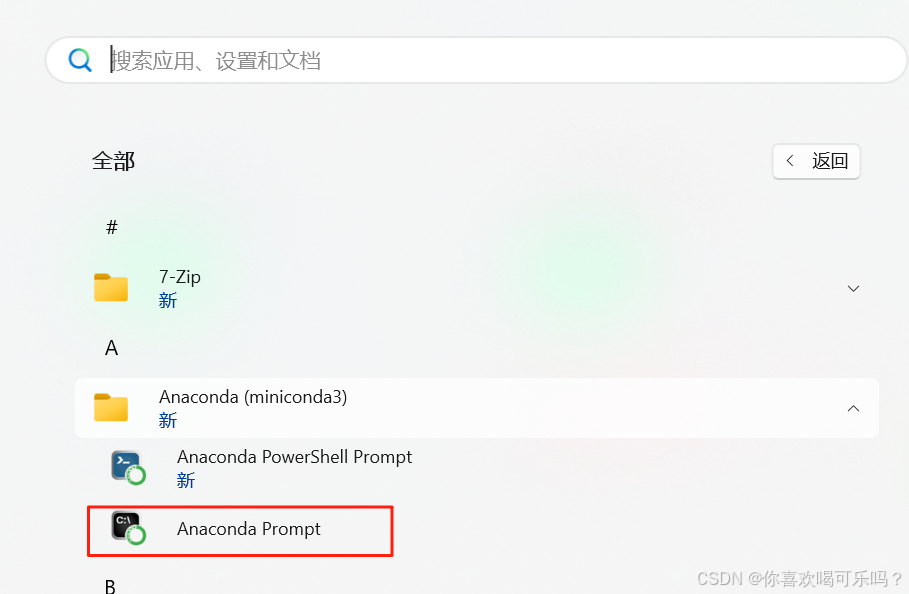

Windows安装Miniconda

一、下载 https://www.anaconda.com/download/success 二、安装 三、配置镜像源 Anaconda/Miniconda pip 配置清华镜像源_anaconda配置清华源-CSDN博客 四、常用操作命令 Anaconda/Miniconda 基本操作命令_miniconda创建环境命令-CSDN博客...

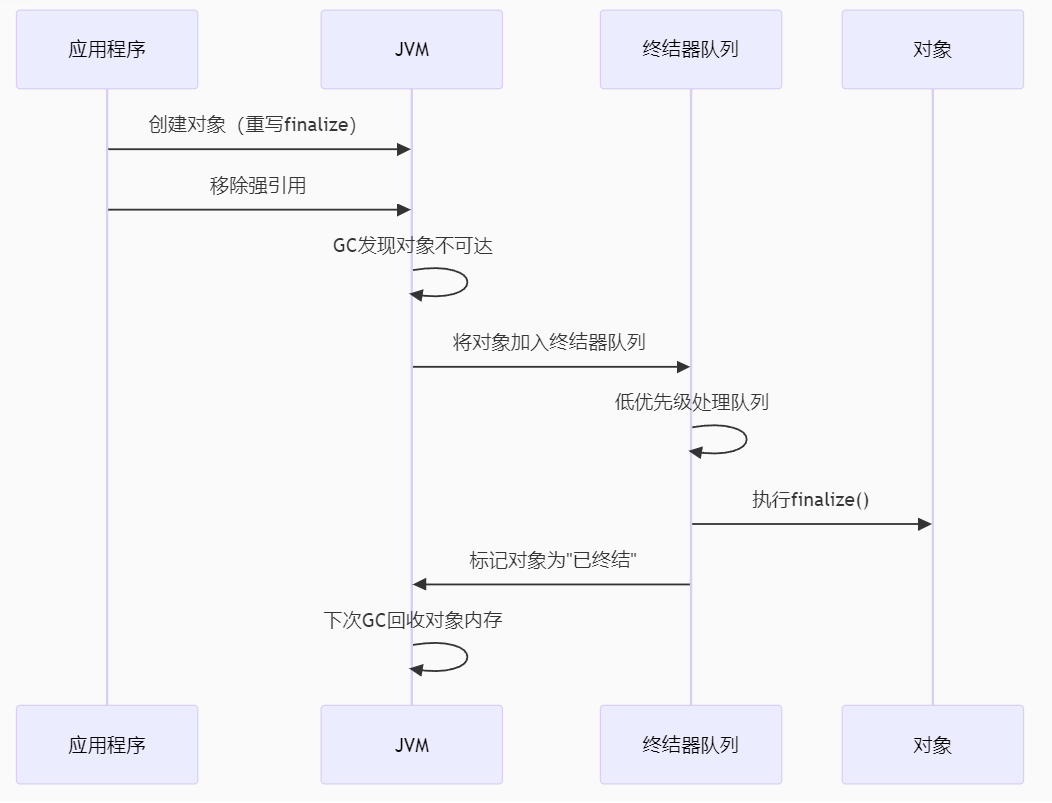

【 java 虚拟机知识 第一篇 】

目录 1.内存模型 1.1.JVM内存模型的介绍 1.2.堆和栈的区别 1.3.栈的存储细节 1.4.堆的部分 1.5.程序计数器的作用 1.6.方法区的内容 1.7.字符串池 1.8.引用类型 1.9.内存泄漏与内存溢出 1.10.会出现内存溢出的结构 1.内存模型 1.1.JVM内存模型的介绍 内存模型主要分…...

STM32---外部32.768K晶振(LSE)无法起振问题

晶振是否起振主要就检查两个1、晶振与MCU是否兼容;2、晶振的负载电容是否匹配 目录 一、判断晶振与MCU是否兼容 二、判断负载电容是否匹配 1. 晶振负载电容(CL)与匹配电容(CL1、CL2)的关系 2. 如何选择 CL1 和 CL…...