CPU组成元素:运算器+控制器

目录标题

- 一、计算机硬件组成概述(Introduction to Computer Hardware Components)

- 1.1 计算机系统的基本构架(Basic Architecture of Computer Systems)

- 1.2 CPU的组成

- 1.3运算器(Arithmetic Unit)、控制器(Control Unit)及内部寄存器(Internal Registers)的地位与作用

- 1.4 计算机发展史上的经典硬件组成方案(Classic Hardware Composition Schemes in the History of Computer Development)

- 二、运算器详解(A Detailed Study of Arithmetic Unit)

- 2.1 算术逻辑单元(ALU,Arithmetic and Logic Unit)

- 2.2 累加寄存器(Accumulator)

- 2.2.1 加法和减法运算

- 2.2.2 乘法迭代与 ALU 配合

- 2.2.3 内存操作与数据移动

- 2.3 数据缓冲寄存器 (Data Buffer Register)

- 功能与应用

- 2.4 状态条件寄存器 (Status Condition Register)

- 三、控制器全解析(An In-depth Analysis of Control Unit)

- 3.1 指令寄存器 (Instruction Register)

- 功能与特点

- 3.2 程序计数器 (Program Counter)

- 功能与特点

- 3.3 地址寄存器 (Address Register)

- 功能与应用

- 3.4 指令译码器 (Instruction Decoder)

- 功能与特点

- 3.5 控制单元 (Control Unit)

- 功能与特点

- 3.6 控制器的任务与功能(Tasks and Functions of Control Units)

- 3.7 微指令与微程序控制(Microinstructions and Microprogram Control)

- 1. 微指令详解

- 2. 微程序控制

- 3.8 硬布线控制器(Hardwired Control Units)和微编程特性控制器(Microprogrammed Feature Control Units)的设计与性能对比

- 3.8.1 硬布线控制器(Hardwired Control Units)

- 3.8.2 微编程特性控制器(Microprogrammed Control Units)

- 四、深入浅出内部寄存器(Demystifying Internal Registers)

- 4.1 寄存器的分类与应用(Classification and Application of Registers)

- 4.2 内部寄存器的结构与操作(Structure and Operations of Internal Registers)

- 4.3 寄存器堆(Registers Stack)在高性能计算机中的作用与实现

- 1.寄存器堆的构造和原理

- 2.寄存器堆应用领域及其优势

- 3. 寄存器堆实现方式

- 五、计算机硬件的高级应用(Advanced Applications of Computer Hardware)

- 5.1 多媒体指令集扩展(Multimedia Instruction Set Extensions)对硬件组成的改进

- 5.2 多核处理器(Multi-core Processor)的设计原理与优势

- 5.2.1 设计原理

- 5.2.2 优势

- 5.3 多线程(Multithreading)

- 抢占式多任务处理

- 协作式多任务处理

一、计算机硬件组成概述(Introduction to Computer Hardware Components)

1.1 计算机系统的基本构架(Basic Architecture of Computer Systems)

计算机系统可以分为五大部分:输入设备、输出设备、中央处理器(Central Processing Unit, CPU)、主存储器和辅助存储器。其中,CPU 是整个计算机系统的核心部件,负责执行与控制各种运算并协调其他硬件组件的工作。CPU 又分为运算器(Arithmetic Unit)和控制器(Control Unit),两者共同完成程序指令和数据的处理。

运算器主要用于进行各种数值和逻辑运算,包括加减乘除、与或非等操作;控制器则负责从主存中获取指令及相关数据,并决定如何对这些指令进行翻译和执行,以维持计算机系统的正常运行。此外,还有内部寄存器(Internal Registers),它们位于 CPU 内部,旨在提供高速临时存储,以便 CPU 快速地访问和操作数据。

通常情况下,计算机硬件设计遵循一种统称为“冯·诺依曼体系结构”的基本原则,即将存储器与处理器分离,采用一条总线连接不同的硬件部件。但是,随着计算机技术的发展,硬件组成方案在历史上也出现了很多变革和创新。

1.2 CPU的组成

CPU(中央处理器,Central Processing Unit)是计算机系统中负责执行程序指令和数据运算的核心部件。一个典型的 CPU 通常包括以下几个主要组成部分:

- 控制单元:控制单元负责从内存中获取待执行的指令并解码、译码。它还负责生成相应的操作命令以调度其他硬件组件(例如寄存器、内存等)。控制单元主要由以下部件构成:

- 指令寄存器 (Instruction Register)

- 程序计数器 (Program Counter)

- 地址寄存器 (Address Register)

- 指令译码器 (Instruction Decoder)

- 运算器:运算器负责处理各种数字信号及逻辑操作,如加法、减法、乘法、除法、移位等。以下部件属于运算器的重要构成:

- 算术逻辑单元 (Arithmetic and Logic Unit, ALU)

- 累加寄存器 (Accumulator)

- 数据缓冲寄存器 (Data Buffer Register)

- 标志寄存器 (Flag Register)

- 寄存器集:寄存器用于存储临时信息,增强 CPU 计算能力。寄存器类型有很多,根据功能可划分为:

- 通用寄存器

- 数据寄存器

- 状态寄存器

- 特殊功能寄存器(如栈指针或者基址)

- 高速缓存:为降低 CPU 与内存之间访问速度的差异,提高效率,部分 CPU 设计中还包含一定空间的高速缓存。它可以暂时存储近期频繁使用的数据或者代码块,便于快速调用。

这些组件共同协同工作,使 CPU 能够有效地执行程序代码、处理各种算术和逻辑任务以及存取数据等。需要注意的是,不同架构的 CPU (例如 RISC 和 CISC)在性能和复杂度上可能会有所差异,具体实现细节亦相应发生变化。同时, CPU 技术在不断演进,随着制程技术的不断改进,CPU 在能源消耗和运行速度方面也正在不断优化。

1.3运算器(Arithmetic Unit)、控制器(Control Unit)及内部寄存器(Internal Registers)的地位与作用

在计算机中,运算器(Arithmetic Unit)、控制器(Control Unit)和内部寄存器(Internal Registers)是处理器(Processor)的主要组成部分。这些组件共同完成计算、执行指令以及维护在程序执行过程中的数据。

以下是它们各自的作用:

- 运算器(Arithmetic Unit)

运算器负责执行所有算术和逻辑运算。例如,加法、减法、乘法、除法等。此外,它还处理与位操作相关的任务,如 And、Or 和 Not 等。运算器对应的硬件单元称为算术逻辑单元(Arithmetic Logic Unit, ALU)。在 CPU 中,ALU 是一块高度集成的电路,负责按照输入信号和控制信号执行特定的操作。 - 控制器(Control Unit)

控制器负责管理计算机执行指令的整个过程。其核心功能包括获取一个指令,解码这个指令,并将其分配给相应的处理模块(如 ALU 或其他设备)进行处理。控制器会发出各种控制信号来协调工作,使得各个部分协同完成任务。简而言之,控制器在 CPU 中担任“大脑”的角色。 - 内部寄存器(Internal Registers)

内部寄存器是 CPU 使用的一些高速存储单元。它们用于保存和传输在程序执行过程中产生的数据,例如算术和逻辑操作的结果、指针地址和内存里的数据等。寄存器允许 CPU 快速访问这些数据,而无需访问相对较慢的主内存(RAM)。根据寄存器的功能,可以将其分为通用寄存器、专用寄存器和条件编码寄存器。

这三个组件共同担任计算机核心处理的任务,协同完成整个系统的运算、控制以及支持程序执行所需的临时数据交换工作。通过密切协作,它们使处理器能够快速高效地执行各种程序代码。

1.4 计算机发展史上的经典硬件组成方案(Classic Hardware Composition Schemes in the History of Computer Development)

| 代数 | 时间段 | 主要元件 | 代表机型 | 特点 | 运算器、控制器、内部寄存器 |

|---|---|---|---|---|---|

| 第一代 | 1940s - 1950s | 电子管 | ENIAC, EDVAC | 体积庞大,耗能巨大,运行速度慢,寿命短 | 采用真空管实现,功能简单,性能有限 |

| 第二代 | 1950s - 1960s | 晶体管 | IBM 7090, CDC 1604 | 小型化,功耗降低,运行速度提升 | 晶体管替代真空管,功能得到加强,性能有所提高 |

| 第三代 | 1960s - 1970s | 集成电路(IC) | IBM System/360, DEC PDP-8 | 规模更小,运行速度更快,性能更高,成本更低 | IC设计开始应用于处理器,进一步增强功能和性能 |

| 第四代 | 1970s - 至今 | 大规模集成电路 | 英特尔8086处理器 | 高度集成度,大容量存储器,个人电脑普及 | 高度复杂的处理器设计,强大的功能与性能 |

从第一代计算机(真空管时代)到现在的第四代计算机(大规模集成电路时代),运算器、控制器和内部寄存器在设计和实现方面都经历了明显的变革。随着技术的进步,这些重要组件日益复杂且高性能。

二、运算器详解(A Detailed Study of Arithmetic Unit)

| 结构部分 | 功能说明 |

|---|---|

| 算术逻辑单元(ALU) | 执行算术和逻辑运算,如加法、减法、乘法、除法等 |

| 累加寄存器(AC) | 临时存储计算中间结果,在连续的数学计算任务中起核心作用 |

| 数据缓冲寄存器 (DBR) | 在 CPU 和其他计算机组件之间暂时存储和传输数据,降低了数据传输延迟 |

| 状态条件寄存器 (SCR) | 存储 CPU 中各种事件和操作状态信息,提供条件判断依据以决定接下来执行的指令 |

这个表格总结了运算器的四个主要组成部分及它们各自的功能。这些部分共同构成了运算器,使其能够有效地执行不同类型的计算和逻辑操作。

2.1 算术逻辑单元(ALU,Arithmetic and Logic Unit)

算术逻辑单元(ALU,Arithmetic and Logic Unit) 是计算机的核心部件之一,用于对数据进行算术和逻辑操作。ALU 的主要功能包括:加法、减法、乘法、除法、移位(Shift)、取反(NOT)、以及其他逻辑运算如 AND、OR 和 XOR。通过这些基本操作,ALU 能够实现复杂数学运算以完成各种任务需求。

ALU 的基本结构由以下部分组成:

| 结构部分 | 功能说明 |

|---|---|

| 数据输入端口(Data Input Ports) | 接收来自寄存器或其他硬件设备的数据 |

| 控制输入端口(Control Input Ports) | 接收指令,控制 ALU 执行哪个操作 |

| 数据输出端口(Data Output Ports) | 发送经过处理的结果给内部寄存器或其他硬件设备 |

| 标志寄存器(Flag Register) | 记录运算结果的特性,辅助评估和调整连续运算 |

此表格展示了ALU的基本结构以及各部分的功能。ALU主要负责执行算术和逻辑运算,并与其他计算机组件进行通信以接收数据、发送指令和返回结果。标志寄存器用于记录有关D运算结果的信息,在程序中实现更精确的控制。

2.2 累加寄存器(Accumulator)

累加寄存器是一种特殊类型的数据寄存器,作为 CPU 内部的重要组件,在算术和逻辑操作中扮演核心角色。它用于临时存储计算的中间结果,从而方便处理器高效地执行连续的数学计算任务。

以下是累加寄存器在不同场景下的应用:

2.2.1 加法和减法运算

在执行加法或减法运算时,累加寄存器可以充当一个操作数的角色。例如,对于 A + B 或 A - B 的计算,使用两个输入寄存器 (A 和 B) 并将其结果放入累加寄存器中。累加寄存器有助于简化硬件设计,并使得多次叠加或求差更为直接。

2.2.2 乘法迭代与 ALU 配合

在执行乘法操作时,累加寄存器也可用于存储迭代的中间结果。循环第 N 次乘法过程中,累加寄存器保存前 N-1 次乘法结果;待每轮乘法结束后,累加寄存器会更新相应数据——将原始值加上新产生的部分积。最终,累加寄存器里存储的即为乘法运算结果。

2.2.3 内存操作与数据移动

累加寄存器还可参与内存和寄存器之间的数据传输。在存储和加载任务中,它暂时存放需要被写入或读出的数据,方便总线进行有序的信息交换。

综上所述,累加寄存器对于高效处理各种数学和逻辑计算是至关重要的。实际应用中,CPU 架构设计者会根据性能目标以及资源限制调节累加寄存器的位数、特性和其他参数。例如,在现代 CPU 中可能存在多个累加寄存器,赋予设备更强大的并行计算功能。

2.3 数据缓冲寄存器 (Data Buffer Register)

数据缓冲寄存器(Data Buffer Register,简称 DBR)也是计算机内部的一种特殊寄存器。它的主要功能是在 CPU 和其他计算机组件(如内存或输入/输出设备)之间暂时存储和传输数据。

功能与应用

- 降低数据传输延迟:快速临时存储器提高了计算机在读写操作中的效率。接收到的数据将首先存入数据缓冲寄存器,再由处理器进行进一步操作,有效减少指令等待时间。

- 流水线处理:通过使用数据缓冲寄存器,可以实现多个操作同时进行的并行处理架构,加速计算过程。

- 保持高性能:当系统中可用资源有限时,数据缓冲寄存器作为预加载存储器可以保证处理器的稳定性能。例如,在处理大量数据传输任务时,缓存可以有效地防止处理器过载。

- 协同工作: 在某些情景下,CPU 需要对外部设备发出命令并接收响应。此时, 数据缓冲寄存器将起到一个中介作用,确保双向通信得以顺利完成。

总的来说,数据缓冲寄存器在数据和指令之间搭建了高速通道,将内部计算与外部操作协同调整。这种处理策略大大提高了运算效率,并为系统优化提供更多灵活性。

2.4 状态条件寄存器 (Status Condition Register)

状态条件寄存器(Status Condition Register,简称 SCR 或者 SR)是一种特殊的寄存器,用于存储 CPU 中发生的各种事件和操作的状态信息。这些信息有助于程序了解当前运行环境以及上一个指令执行结果的特征,从而有条件地决定接下来应执行哪些指令。

状态条件寄存器通常包含以下几个常见标志位:

- 零标志(Zero Flag, ZF):如果上一个算数或逻辑操作的结果等于零,零标志置 1,否则置0。该标志在进行比较和测试等操作时非常有用。

- 进位标志(Carry Flag, CF):当无符号整数加法或减法导致进位或借位时,进位标志置为 1。这有助于检测溢出现象,同时也可以方便地实现多精度运算。

- 溢出标志(Overflow Flag, OF):对于二补码表示法,有符号整数的加法或减法可能导致溢出。此时,溢出标志会设置为 1。通过检查 OF 是否为 1,程序可以对溢出情况作出响应处理。

- 负标志(Negative Flag, NF):当最近一次算术或逻辑操作的结果为负数时,负标志置为 1。这使得程序可以在不同的场景下根据 NF 的值作出相应处理。

- 辅助进位标志(Auxiliary Carry Flag, AF):该标志用于BCD(Binary Coded Decimal)运算。当从四位二进制数进行加法操作产生进位(即低半字节向高半字节进位大于 3 时),辅助进位标志置 1。

状态条件寄存器的一些其他功能可能因具体 CPU 架构而异。然而,通常情况下,它们都起到了记录和指示特定事件发生的关键作用。现代编程语言会针对这类系统状态提供控制结构,例如条件跳转、循环等,有助于实现更精细化的流程控制。

三、控制器全解析(An In-depth Analysis of Control Unit)

| 结构部分 | 功能说明 |

|---|---|

| 指令寄存器(IR) | 临时保存当前正在执行的指令,并将解码后的操作命令传递给其他硬件模块 |

| 程序计数器(PC) | 跟踪待执行的指令顺序,支持跳转和循环操作,协作处理中断事件 |

| 地址寄存器(AR) | 存储内存地址,实现基址/索引寻址等方式,与其他控制单元组件一起协调内存管理 |

| 指令译码器(ID) | 解析原始指令并提取信息,生成相应的操作命令,处理条件分支和循环操作 |

这个表格总结了控制器的四个主要组成部分及它们各自的功能。这些部分共同构成了控制器,使其能够有效地调度不同计算机硬件、执行程序代码并完成各种复杂任务。

3.1 指令寄存器 (Instruction Register)

指令寄存器(Instruction Register,简称 IR)是计算机控制器的重要组成部分之一。其主要作用是临时存储当前正在执行的指令,并通过解码后将相应操作命令传递给其他相应硬件模块。

功能与特点

- 保存指令:每当有新指令需要被执行时,指令首先会从内存加载到指令寄存器中。这有助于确保即时且有效地处理各种程序指令。

- 解码与流程控制:在指令寄存器中,原始指令通常需经过解码,以便 CPU 根据指令格式了解并发送相关操作信号。此外,根据具体指令类型和目的,指令寄存器还可以影响其他控制信号生成,从而实现更复杂的功能。

- 协同管理资源:指令寄存器中的指令可能涉及多个计算机硬件单元进行协同工作。因此,CPU 需要利用指令寄存器来调度各种操作,确保运算任务得以顺畅完成。

综上所述,在计算机系统中,指令寄存器对于保持指令处理的高效和连贯性具有关键作用。它与其他模块相互协同工作,执行程序代码并完成各种复杂任务。在实际应用中,指令寄存器的设计和特性还可能因不同 CPU 架构、技术或配置而略有差异。

3.2 程序计数器 (Program Counter)

程序计数器(Program Counter,简称 PC)是控制单元的另一个关键组件。它负责保存计算机即将执行的下一条指令的内存地址,并在每次取出并执行一条指令后实时更新这个地址值。

功能与特点

- 跟踪指令顺序:程序计数器的基本功能是按照预定顺序来获取所有待执行的指令。当处理器完成当前指令的执行之后,程序计数器会自动加位,以指向下一条指令的内存地址。

- 支持跳转和循环:也有可能需要 CPU 跳过某些序列中不准备执行的指令或者为条件分支、循环等重复多次地执行同一段代码。此时,程序计数器可以通过接收外部信号——如分支或跳转命令——来改变其值,并使处理器从指定地址加载新指令。

- 协作中断处理:为应对可能发生的意外事件,程序计数器会配合中断处理机制共同应对。一旦中断发生,程序计数器会暂时保存当前的执行位置(内存地址),然后跳转至异常处理程序。中断处理完成后,程序计数器将被恢复到原先的状态,使处理器继续执行中断前遗留的任务。

总之,程序计数器作为指令调度和地址导航的核心设备,发挥着至关重要的作用。在现代处理器设计中,程序计数器等控制器部件采用了更加先进的技术方案,可实现超标量、多线程并发识别等高级功能,进一步丰富系统性能以满足日益复杂的应用需求。

3.3 地址寄存器 (Address Register)

地址寄存器(Address Register,简称 AR)也是控制单元内部的一个重要组成部分。它主要用于保存和处理与内存相关的地址信息,以便计算机能够正确地在内存中存取数据。

功能与应用

- 存储内存地址:地址寄存器用于临时保存内存中数据或指令所对应的地址。这使得计算机能够按照预定顺序执行任务,并确保数据在内存之间的有序传输。

- 实现基址寻址:一些 CPU 架构支持通过将地址寄存器值与某个基数相加来确定内存单元地址。这种方式称为基址寻址,可以实现更灵活的内存管理策略。

- 索引寻址:类似于基址寻址,在索引寻址中,系统会根据地址寄存器中的值和另一个寄存器(如累加器)的偏移量来计算目标存储位置。这种方法在访问数组和表格等数据结构时非常方便。

- 提供快速响应: 在进行高速运算过程中,地址寄存器确保内存操作迅速响应并跳转至下个目标位置。由此可见,地址寄存器对优化计算效率具有重要意义。

- 协调内存管理:地址寄存器的工作同其他控制单元组件(如程序计数器、指令寄存器等)是息息相关的。在执行过程中,它们各自发挥独特作用以确保指令和数据传递的正常运行。

总之,地址寄存器是控制单元中的关键部件之一,负责处理来自不同内存位置的信息。这类寄存器根据具体CPU架构和使用需求可能涉及多种类型,例如段寄存器、页表基址寄存器等。

3.4 指令译码器 (Instruction Decoder)

指令译码器(Instruction Decoder,简称 ID)是控制单元中负责解析和翻译指令的关键部件。它能够将从指令寄存器接收到的原始指令进行解码,然后生成一系列相应的操作命令,指导计算机内部硬件执行特定任务。

功能与特点

- 指令解码:指令译码器的核心功能是对原始指令进行解码以提取所需信息。每条指令都包含了用于描述操作类型、操作数和其他参数的代码。指令译码器通过逐个分析这些片段,识别原始程序的真实意图。

- 生成操作命令:经过解码之后,指令译码器会根据得出的结果生成对应的控制信号。这些信号进而驱动处理器、寄存器、内存等组件按照预期动作执行任务。

- 条件分支处理:在执行条件分支或循环操作时,指令译码器需要结合状态条件寄存器的当前状态来确认下一步应该进行哪种操作。计算机可以利用这种方式实现高级编程结构,比如 if-else 或 while 等逻辑语句。

- 协同工作:指令译码器与其他控制器组件(如程序计数器和地址寄存器)通力合作,确保有序地执行各项任务。例如,在解码过程中,指令译码器可能会需要地址寄存器提供必要的内存访问信息。

总之,指令译码器起到了很强的纽带作用,将编写的代码与计算机硬件系统紧密联系在一起。它负责构建明确、准确的操作命令,有效克服语义歧义问题,并最终引导完成任何任务。

3.5 控制单元 (Control Unit)

控制单元(Control Unit)是计算机 CPU 的核心组成部分之一,负责对各种指令进行解码及产生相应的控制信号,从而调度各个硬件模块有序地参与运算过程。

功能与特点

- 指令解码:CPU 需要通过控制单元解析从内存加载到指令寄存器中的指令内容,并确定操作目标以便生成适当的控制信号。

- 控制时序:控制单元会根据相关指令的需求和约束搭建整个计算任务的时间结构,确保正确处理输入输出以及硬件间通信等动作。

- 资源调度与协同管理:控制单元需要掌握全局信息,在不同系统模块之间安排高效联动,使得功能执行符合预期。

- 流程转换:通过监控系统状态和响应指令变化,控制单元可以切换数据路径或操作模式,实现更加灵活的任务处理。

控制器是计算机中关键部件之一,在高速执行代码和确保硬件资源的完美协同方面发挥了核心作用。在不同设备的 CPU 中,控制单元的具体实现方法及特性可能有所差异,但总体上讲,该组件始终负责为整个系统提供稳定、精准和可靠的指令处理支持。

3.6 控制器的任务与功能(Tasks and Functions of Control Units)

控制器,顾名思义,就是负责在计算机系统中协调和管控各种操作的部件。它主要有以下任务和功能:

- 指令获取与执行:控制器会从内存中按顺序读取并解码程序的指令,然后根据指令的类型来确定接下来的操作。这包括算术逻辑运算和处理器线程之间的通信等。

- 数据传输控制:控制器需要管理数据在计算机系统的不同部分之间的传输过程,例如把数据从寄存器传到内存,或者从内存传回寄存器。

- 时序管理:为确保计算机硬件组件能正确地协同工作,控制器需确保遵循特定的时序约束,以便所有指令都能按照预期进行。

- I/O 设备控制:控制器还需要对输入/输出设备进行控制。比如开始/停止设备运转,监测缓冲区是否已满等。

- 中断处理及异常处理:当外部事件(如用户输入)或者异常情况(如除数为零时的除法操作)发生时,控制器需要暂停正在执行的任务,解决这些问题,然后再恢复。

总之,控制器是计算机硬件组成中的一个关键部分,具有自动协调、控制和管理整个计算机系统各种操作的功能。

3.7 微指令与微程序控制(Microinstructions and Microprogram Control)

在现代计算机系统中,针对控制器的操作和决策过程经常采用微指令和微程序。微指令是一种更基本、更小的执行单位,它们实现了对硬件组件进行分步、精细控制的功能。这些微指令按照特定的顺序排列形成为微程序,从而完成所需的复杂任务。

1. 微指令详解

微指令(Microinstruction) 是计算机领域中指令集层次结构中的最底层指令。这些微指令直接支配计算机的硬件部件,并由高级指令驱动。每一个高级指令都能够被拆解成若干个具有实际执行能力的微指令。

许多计算机体系结构使用微指令来规范化低级别的处理操作,包括数据榨取、寻址方式和总线控制等。通过支持多达数百上千种不同类型的微指令,同时控制各种硬件资源,微指令极大地丰富了计算设备的运作灵活性。

2. 微程序控制

微程序控制(Microprogram Control)是将计算机指令层次体系结构中的底层微指令进行排列整合,形成可实现有针对性任务的程序。一个微程序通常包含多个微指令,并按照特定顺序依次执行。

微程序控制是一种更加灵活和高效的控制方法。它允许设计者根据硬件资源创建不同颗粒度的功能模块,并通过编写针对这些模块的微指令来实现复杂处理。在计算机系统中,采用微程序控制可以极大提高电路性能和运行速度,减少硬件控制逻辑的复杂性。

3.8 硬布线控制器(Hardwired Control Units)和微编程特性控制器(Microprogrammed Feature Control Units)的设计与性能对比

控制器是计算机中负责管理和协调其他各个部分配合工作的核心部件,目前有两种主要类型的控制器:硬布线控制器(Hardwired Control Units)和微编程特性控制器(Microprogrammed Control Units)。了解这两者之间的差异非常重要,因为它们代表了不同的计算机硬件设计思路。

3.8.1 硬布线控制器(Hardwired Control Units)

硬布线控制器直接将指令集硬编码到硬件中,由底层物理电路实现,这种方式具有较高的执行速度和稳定性。但缺点是更改功能会非常困难,需要重新设计整个控制器部分。

特点:

- 高效:指令执行快速;

- 稳定性高:不存在错误译码的概率;

- 更改指令集困难,修改内部功能相对复杂;

- 设计时需投入较多精力。

3.8.2 微编程特性控制器(Microprogrammed Control Units)

微编程特性控制器采用存储在只读存储器(ROM)中的微指令来控制计算机。这些微指令以底层逻辑门电路为基础,执行复杂操作的同时具备较强的灵活性。

特点:

- 容易进行扩展和更改指令集;

- 支持多种指令集:统一ROM容易实现多个功能并在其间切换;

- 灵活性高:方便更新指令集及软件优化;

- 相对硬布线控制器性能可能稍逊一筹。

结论:

硬布线控制器和微编程特性控制器各有利弊,视具体应用需求和开发资源而定。若追求高执行速度和稳定性,可选择硬布线控制器;对于需要常常调整、升级或存在多种指令集版本的情况,则使用微编程特性控制器更合适。随着技术进步,未来或将找到完美兼顾两者优点的新设计。

四、深入浅出内部寄存器(Demystifying Internal Registers)

4.1 寄存器的分类与应用(Classification and Application of Registers)

寄存器是计算机中一种非常重要并且高速的存储单元,通常位于处理器(如 CPU)内部。根据功能和使用场景,我们可以将寄存器分为以下几类:

- 数据寄存器(Data Register):此类寄存器专门用于存储处理器需要执行计算的数据。例如,在表示数值时可能会用到的累加器(Accumulator),以及在多功能寄存器组中存在的通用寄存器(General Purpose Register)。

- 地址寄存器(Address Register):地址寄存器负责存储其他存储设备的物理内存地址,如程序计数器(Program Counter, PC)、堆栈指针(Stack Pointer)等。这些寄存器在实际应用中协助处理器访问相关数据项。

- 状态寄存器(Status Register)/标志寄存器(Flag Register):状态寄存器主要用于记录各种运算结果的特征,例如零位(Zero flag)、进位位(Carry flag)、溢出位(Overflow flag)等。根据这些标志位可以帮助决策系统调整程序流程或检查错误。

- 控制寄存器(Control Register):控制寄存器主要包含系统控制信息,例如指示处理器的当前运行模式(保护模式或实地址模式)、开启或关闭中断等。

4.2 内部寄存器的结构与操作(Structure and Operations of Internal Registers)

内部寄存器是计算机中用于临时存储数据和状态信息的高速小容量存储器。它们位于 CPU 内部,直接对运算器和控制器进行支持。以下是内部寄存器的主要结构和操作。

- 结构(Structure):寄存器由存储单元组成,每个存储单元可保存一个比特(bit)。一个 n 比特的寄存器能够表达 2^n 种不同的状态。实际应用中,根据处理器采用的指令集体系架构 (ISA),寄存器的位宽可能范围为 8 位、16 位、32 位,甚至到最现代的 64 位或更多。

- 读操作(Read Operation):从寄存器中读取信息的过程。在执行此操作时,寄存器将输出存储的信息到外部总线或其他设备,而原始数据保留在寄存器中,不会被清除。

- 写操作(Write Operation):向寄存器中写入数据的过程。在执行此操作时,寄存器将新数据存储在内部,并覆盖先前存储的数据。写操作可以通过设置相应的控制信号来完成。

- 复位(Reset):将寄存器内的所有比特设置为预定值(通常为 0 或其它特定值)。此操作将清除寄存器中当前存储的数据,保证从事先定义的状态开始执行计算。

- 输出使能(Output Enable):通过在特定时钟周期激活输出信号,将寄存器里存储的数据发送至目标设备。这种操作技术可以与读操作相结合,以进行同步访问。

在计算机系统中,内部寄存器非常关键,因为它们极大地提高了处理速度并增强了系统性能。了解内部寄存器的结构和操作方式有助于我们更深入地理解计算机硬件组成和工作原理。

4.3 寄存器堆(Registers Stack)在高性能计算机中的作用与实现

寄存器堆(Registers Stack)是一种特殊类型的寄存器组织,它在高性能计算机系统中起着关键作用。将多个寄存器有序排列在运算器内部,形成一个连续可快速访问的存储空间。

1.寄存器堆的构造和原理

寄存器堆是由一系列寄存器组成,这些寄存器之间可以通过总线或其他结构实现快速连接。相对于传统的单一寄存器系统,寄存器堆具有更高效的数据存取速度和更灵活的配置操作方式。

2.寄存器堆应用领域及其优势

寄存器堆在高性能计算机系统,如超级计算机、图形处理器(GPU)、并行处理器等场景中发挥着重要作用。采用寄存器堆可带来以下优势:

- 提升运算速度:因为寄存器堆增加了可用的临时存储空间,减少了与内存的数据交互,从而大幅度地提高了计算任务的完成速度。

- 支持并发运算与流水线技术:寄存器堆允许同时进行多个运算任务,提高资源使用率并支持流水线技术以进一步增加计算效率。

- 节省内存开销:寄存器堆将部分数据临时存储在距离 CPU 更近的位置,从而减少了对内存的依赖和内存开销。

3. 寄存器堆实现方式

在具体实现上,寄存器堆可以采用以下两种方式:

- 静态寄存器堆:在这种设计中,固定数量的寄存器被硬件制造商预先配置在芯片内部。优点是空间利用稳定、易于管理;但容量受限,可能无法满足某些特定场景的需求。

- 动态可扩展寄存器堆:与上述方法相反,这里的寄存器堆能够根据实际需求进行扩容或缩容。优点是可以为不同应用提供更好的定制化服务;缺点是复杂度较高,很难达到最佳空间利用率。

总之,寄存器堆是计算机硬件系统中一个重要组成部分,在高性能计算领域发挥着至关重要的作用。

五、计算机硬件的高级应用(Advanced Applications of Computer Hardware)

5.1 多媒体指令集扩展(Multimedia Instruction Set Extensions)对硬件组成的改进

随着多媒体处理需求的增长,音频和视频处理已经成为计算机技术领域中至关重要的任务之一。为了更有效地满足这些需求,计算机硬件制造商引入了针对特定多媒体处理任务的指令集扩展。

多媒体指令集扩展可以帮助提高计算机在处理涉及数据并行性的任务时的效率。它们主要是通过 SIMD(Single Instruction Multiple Data,单指令多数据流)执行方式来实现更高效的处理性能。在 SIMD 模式下,一个指令可以同时对多个数据进行操作。这样可以显著降低逐项处理同类数据所需的时间,从而大幅提升处理速度。

例如,Intel 公司推出了 MMX(Multi-Media eXtensions)、SSE(Streaming SIMD Extension) 和 AVX (Advanced Vector Extensions) 等多媒体指令集扩展。而 AMD 公司也推出了如 3DNow!等专门针对多媒体处理任务的指令集扩展。

这些多媒体指令集扩展不仅加速了音频、视频和图像处理任务,还对加密计算、科学计算等领域的性能优化有所贡献。通过引入这些指令集扩展,硬件制造商不断推动着计算机硬件组成的发展与创新。

5.2 多核处理器(Multi-core Processor)的设计原理与优势

随着对高性能计算机系统的需求不断增长,多核处理器(Multi-core Processor)应运而生。相较于单核处理器,多核处理器在同一芯片上集成了多个执行核心,从而显著提升了计算机的处理能力和能效表现。

5.2.1 设计原理

为什么需要选择多核处理器呢?关键在于处理任务可以并行进行。每个核心都是一个独立的处理器单元,具备自己的指令和数据流,甚至有着独立的内部缓存。这使得在同一时间,多个核心可以分别处理各自分配的任务,大幅提高了整体的计算性能。

5.2.2 优势

- 并发性能:多核处理器具有更好的并发性能,因为它们可以同时处理许多任务。类型包括数据模型中的线程级并行处理以及指令级并行处理。

- 扩展性:多核处理器能够轻易适应新技术,并通过添加更多执行核心来扩展其性能。例如,在构建超级计算机时,只需要将若干多核处理器集成在一个微电子板上即可。

- 能效:多核处理器在提供并发性能的同时,优化了能耗。其单元内可调整不同部分的工作速度以最小化功耗,并在可能的情况下通常采取动态调频降压(Dynamic Voltage and Frequency Scaling, DVFS)模式。

- 易编程性:既然通过多个线程或进程可以充分利用多核处理器的优势,许多操作系统和语言现已添加特定地对多核处理器进行优化与支持。

然而,许多应用未能立即从多核处理器中受益,因为它们的算法未经过必要的修改来适应新型硬件环境。ただ、矩阵运算时,如果能开展良好的并行计划设计,则对于某些任务存在明显优势。

5.3 多线程(Multithreading)

多线程是指在一个程序中有多个独立的执行单元运行,这些执行单元称为线程。每个线程拥有自己的专用程序计数器、栈和其他处理器寄存器,但它们共享相同的代码段、数据段和系统资源(如文件、通信端口等)。通过启动多个线程并行工作,可以提高程序的执行效率。

利用多线程分两种模式:抢占式多任务处理和协作式多任务处理。

抢占式多任务处理

抢占式多任务处理由操作系统负责管理,系统决定何时中断一个正在运行的线程并给另一个线程CPU时间。 这样做的目的是确保所有线程公平地获得处理器时间,并最大限度地减少用户感知到的延迟。Java 和 C# 都支持抢占式多线程。

协作式多任务处理

协作式多任务处理要求每个线程主动将处理器控制权交还给系统,从而提供给其它线程使用。Python 的全局解释锁(GIL)就是一种协作式多线程实现方式。

多线程存在的挑战包括:

- 竞态条件:当两个或多个线程同时访问共享资源时,可能导致意外的结果。例如,当多个线程试图同时修改一个变量时,最后的结果可能会因为线程执行顺序而不同。

- 死锁:死锁是指两个或更多线程互相等待彼此释放共享资源,从而导致它们永远无法继续执行。

- 资源滥用:在一些情况下,过多的线程可能导致系统资源(如内存、计算能力)被耗尽。

面对这些挑战,程序员需要使用合适的同步原语(如信号量、互斥器和事件)来确保代码在多线程环境中正确运行。

相关文章:

CPU组成元素:运算器+控制器

目录标题 一、计算机硬件组成概述(Introduction to Computer Hardware Components)1.1 计算机系统的基本构架(Basic Architecture of Computer Systems)1.2 CPU的组成1.3运算器(Arithmetic Unit)、控制器&a…...

计算机网络——主机IP地址、子网掩码、广播地址、网络数、主机数计算方法

目录 一、概念 1.1 主机IP地址 1.2 子网掩码 1.3 广播地址 1.4 子网划分 二、计算 2.1 已知IP地址和子网掩码,计算网络地址和主机地址: 2.2 已知IP地址和子网掩码,计算广播地址: 2.3 已知子网掩码,计算主机数…...

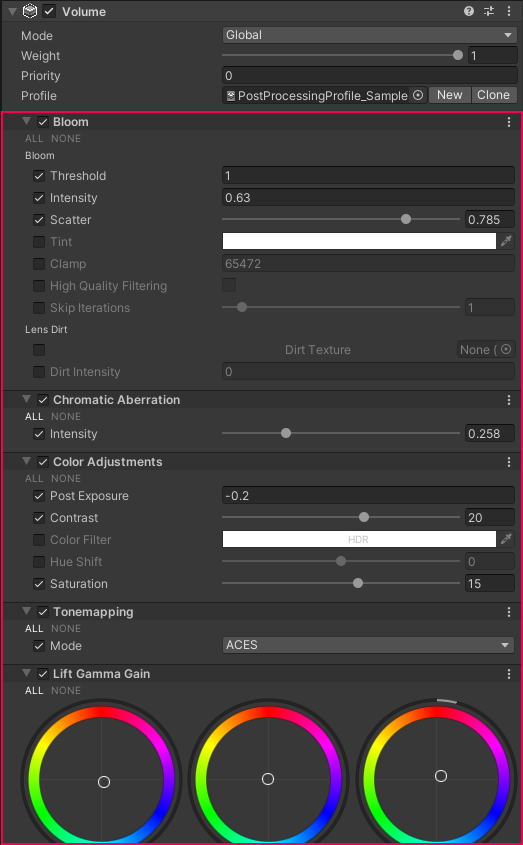

Unity 后处理(Post-Processing) -- (1)概览

在Unity中,后处理(Post-Processing)是在相机所捕捉的图像上应用一些特殊效果的过程,后处理会让图像视觉效果更好(前提是做的好)。 这些效果的范围有非常细微的颜色调整,也包括整体的美术风格的大…...

Ajax + axios + 常用状态码(笔记)

Ajax 求关注😭 一、客户端与服务器相关的概念 1.1 客户端与服务器 1.1.1 服务器 服务器: 负责 存放 和 对外提供 资源 的 电脑本质: 就是一台电脑,只不过 性能 要比别的电脑 高 1.1.2 客户端 客户端: 在上网过程…...

python运算符

本章目的在于帮助大家了解 python中的常用的 算数运算符和赋值运算符 其实 算数运算符就是一些简单运算公式 我们可以编写代码如下 print("1 1 ",11) print("2 - 1 ",2 - 1) print("3 * 3 ",3 * 3) print("4 / 2 ",4 / 2) print(&…...

)

Python 列表(List)

Python中的列表(List)是一种有序的集合,可以包含任意数量的元素,元素可以是数字、字符串或其他对象,甚至包含其他列表。 以下是一些常见的列表操作: 1. 创建列表: 要创建一个列表,可以使用方括号 [] 将元…...

Java设计模式-装饰模式

简介 装饰模式在Java领域是一种常见的设计模式,它能够在不改变对象原有结构的情况下,动态地为对象添加新的功能。它通过封装原有对象,在运行时动态地为对象添加新的行为或者修改原有行为,以扩展对象的功能。这种方式避免了继承的…...

桐乡学历提升-学历到底有什么用呢?

造成“学历和能力,哪个更重要?”的问题,主要是现在有很多人,学历高,而其他方面的能力很差,甚至连基本的生活能力都没有,而更多的人则把有学历就看成有能力,对此现象弄不明白了&#…...

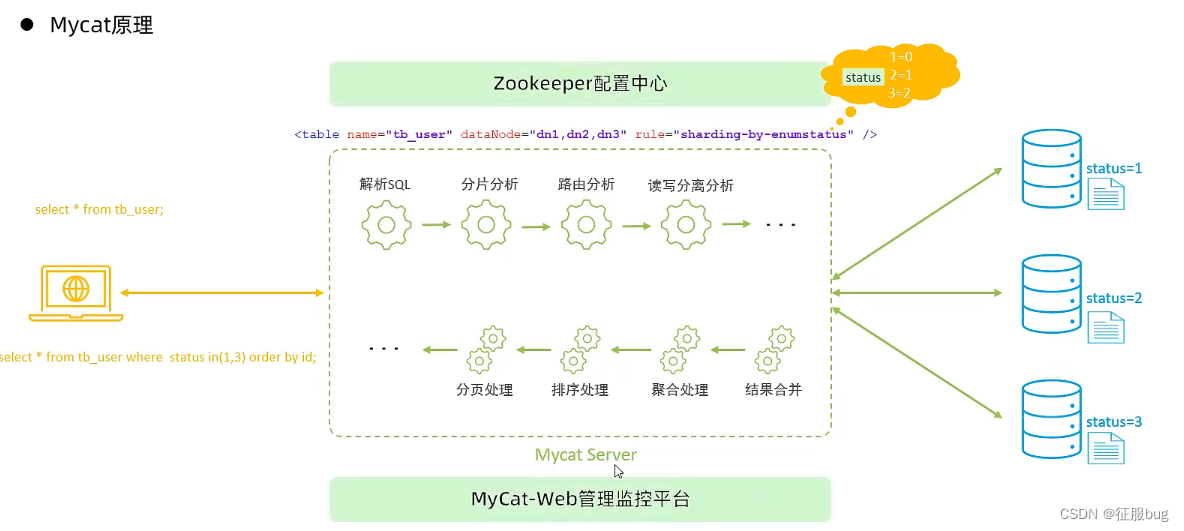

15天学习MySQL计划(运维篇)分库分表-监控-第十四天

15天学习MySQL计划分库分表-监控-第十四天 1.介绍 1.问题分析 随着互联网及移动互联网的发展,应用系统的数据量也是成指数式增加,若采用但数据进行数据存储,存在以下性能瓶颈: IO瓶颈:热点数据太多,数…...

Melis4.0[D1s]:8.显示测试:图片格式和透明度

文章目录 1.准备素材图片1.1 测试图片像素格式的软件RawViewer.exe1.1.1 使用方法 1.2 自己生成测试图片 2.D1s显示引擎介绍(不保证正确)2.1 D1s 可以有2个独立的display device输出(可以同时接2个显示器)2.2 D1s 的 DISP0 有2个通…...

【论文阅读】Pseudo-Labeling and Confirmation Bias in Deep Semi-Supervised Learning

论文下载 GitHub bib: INPROCEEDINGS{,title {Pseudo-Labeling and Confirmation Bias in Deep Semi-Supervised Learning},author {Eric Arazo and Diego Ortego and Paul Albert and Noel E OConnor and Kevin McGuinness},booktitle {IJCNN},year {2020},pages …...

三次输错密码后,系统是怎么做到不让我继续尝试的?

故事背景 忘记密码这件事,相信绝大多数人都遇到过,输一次错一次,错到几次以上,就不允许你继续尝试了。 但当你尝试重置密码,又发现新密码不能和原密码重复: 相信此刻心情只能用一张图形容: 虽…...

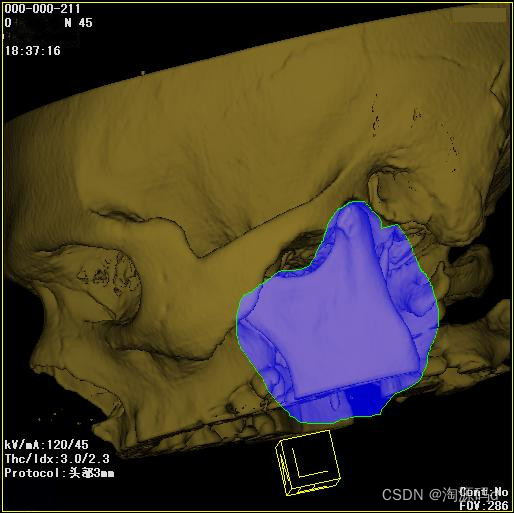

医学影像系统源码,三维后处理和重建 PACS源码

医学影像系统源码,三维后处理和重建 PACS源码 医学影像系统由PACS系统、RIS系统组成,提供与HIS的接口(HL7或其他类型)。 主要功能介绍 信息预约登记 支持对患者、检查项目、申请医生、申请单据、设备等信息进行管理。且支持检查…...

)

golang汇编之函数(四)

基本语法 函数标识符通过TEXT汇编指令定义,表示该行开始的指令定义在TEXT内存段。TEXT语句后的指令一般对应函数的实现,但是对于TEXT指令本身来说并不关心后面是否有指令。我个人觉得TEXT和LABEL定义的符号是类似的,区别只是LABEL是用于跳转…...

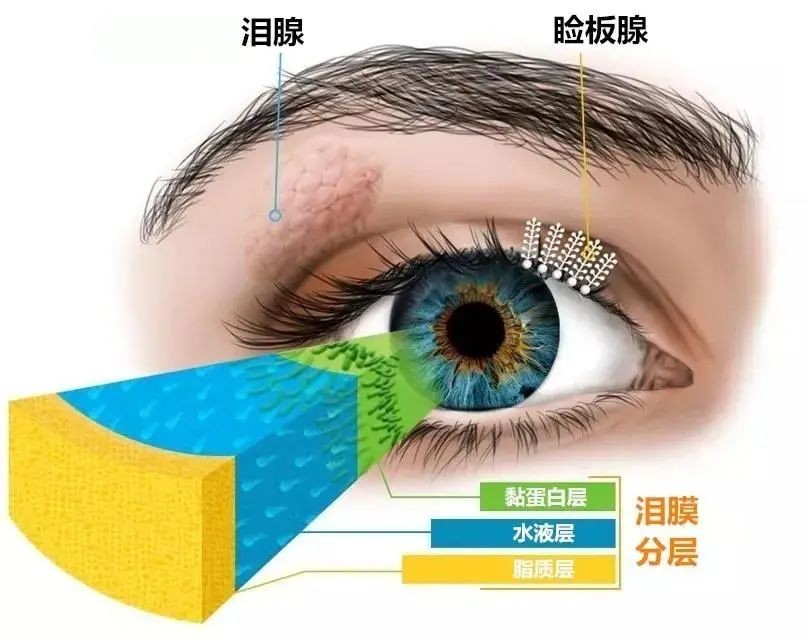

成都爱尔李晓峰主任:眼睛干到发出求救信号,快注意!

眼睛总感觉痒痒的,时不时干涩、酸胀、畏光? 它在提醒你,它太干了救救它! 干眼如何判断? 干眼症是由于泪液的质和量异常或者泪液的流体动力学障碍而导致眼表无法保持湿润的一种眼病。会发生眼睛干涩、酸胀、畏光、灼热感、异物感、看东西容易…...

HiEV独家 | 比亚迪高阶智驾终于来了 ,新款汉首发,多车型将搭载

作者 | 德新 编辑 | 马波 比亚迪上马高阶辅助驾驶,首先从高速NOA开始。 HiEV获悉,今年第三季度,比亚迪将在新的 汉车型 上,搭载高速领航辅助驾驶功能(俗称高速NOA)。继汉之后,王朝系列唐…...

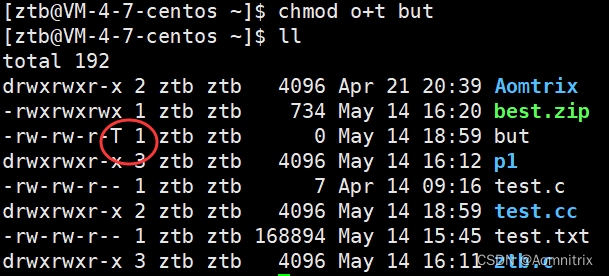

全面解析Linux指令和权限管理

目录 一.指令再讲解1.时间相关的指令2.find等搜索指令与grep指令3.打包和压缩相关的指令4.一些其他指令与热键二.Linux权限1.Linux的权限管理2.文件类型与权限设置3.目录的权限与粘滞位 一.指令再讲解 1.时间相关的指令 date指令: date 用法:date [OPTION]… [FOR…...

C++ enum 和enum class

文章目录 C enum 和 enum class共同点区别 C enum 和 enum class 在C中, enum 是一种定义枚举类型的方法。 一个枚举是一个整数值的命名集合。 可以通过以下方式创建一个枚举类型: enum Color {RED,GREEN,BLUE };这里我们定义了一个名为 Color 的枚举类…...

设计模式之中介者模式

参考资料 曾探《JavaScript设计模式与开发实践》;「设计模式 JavaScript 描述」中介者模式JavaScript 设计模式之中介者模式 定义 在我们生活的世界中,每个人每个物体之间都会产生一些错综复杂的联系。在应用程序里也是一样,程序由大大小小…...

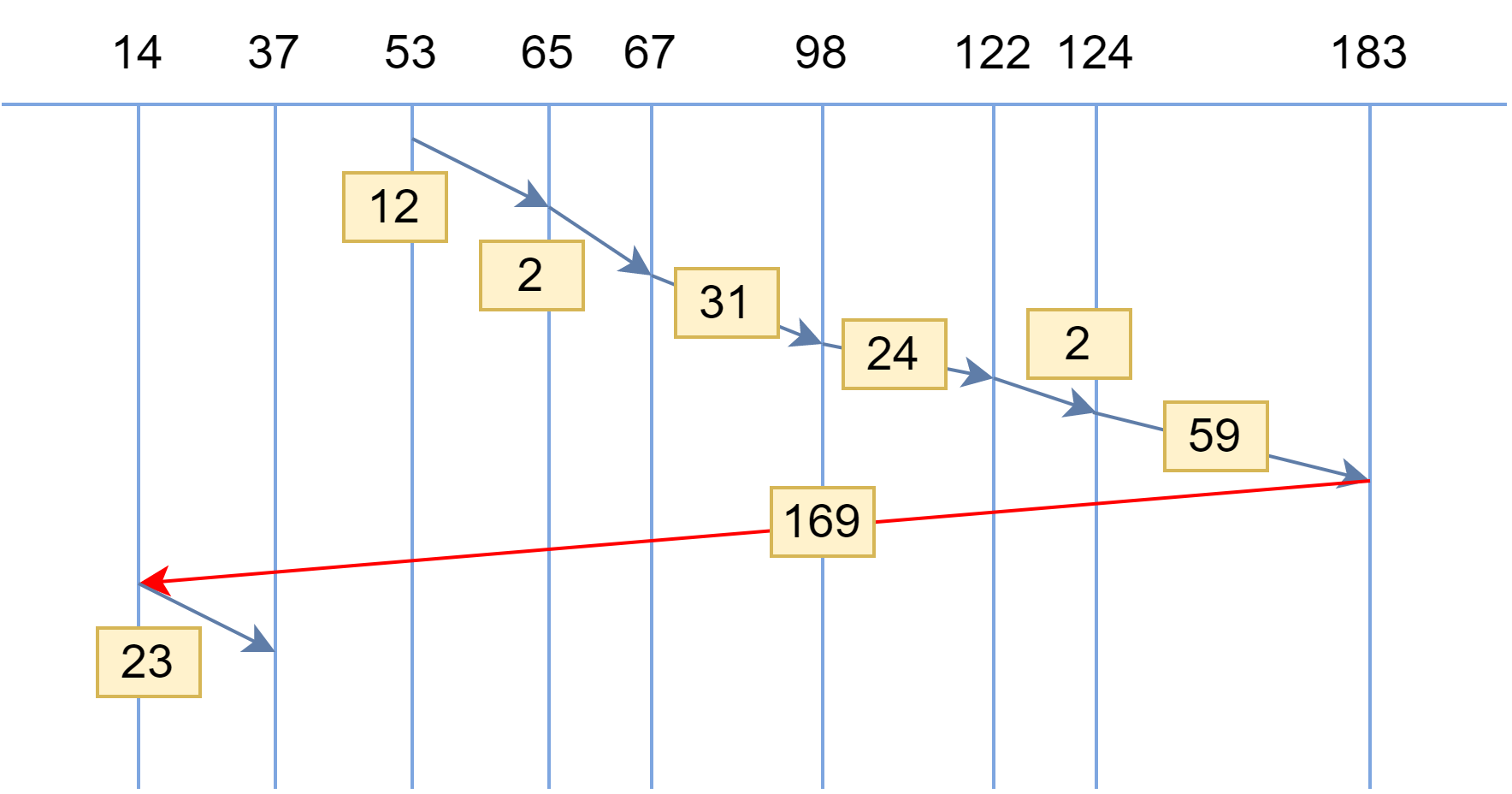

DJ5-8 磁盘存储器的性能和调度

目录 5.8.1 磁盘性能简述 1、磁盘的结构和布局 2、磁盘的类型 3、磁盘数据的组织和格式 4、磁盘的访问过程 5、磁盘访问时间 5.8.2 磁盘调度算法 1、先来先服务 FCFS 2、最短寻道时间优先 SSTF 3、扫描算法(电梯算法)SCAN 4、循环扫描算法 …...

` 方法)

深入浅出:JavaScript 中的 `window.crypto.getRandomValues()` 方法

深入浅出:JavaScript 中的 window.crypto.getRandomValues() 方法 在现代 Web 开发中,随机数的生成看似简单,却隐藏着许多玄机。无论是生成密码、加密密钥,还是创建安全令牌,随机数的质量直接关系到系统的安全性。Jav…...

CRMEB 中 PHP 短信扩展开发:涵盖一号通、阿里云、腾讯云、创蓝

目前已有一号通短信、阿里云短信、腾讯云短信扩展 扩展入口文件 文件目录 crmeb\services\sms\Sms.php 默认驱动类型为:一号通 namespace crmeb\services\sms;use crmeb\basic\BaseManager; use crmeb\services\AccessTokenServeService; use crmeb\services\sms\…...

提升移动端网页调试效率:WebDebugX 与常见工具组合实践

在日常移动端开发中,网页调试始终是一个高频但又极具挑战的环节。尤其在面对 iOS 与 Android 的混合技术栈、各种设备差异化行为时,开发者迫切需要一套高效、可靠且跨平台的调试方案。过去,我们或多或少使用过 Chrome DevTools、Remote Debug…...

c# 局部函数 定义、功能与示例

C# 局部函数:定义、功能与示例 1. 定义与功能 局部函数(Local Function)是嵌套在另一个方法内部的私有方法,仅在包含它的方法内可见。 • 作用:封装仅用于当前方法的逻辑,避免污染类作用域,提升…...

HTTPS证书一年多少钱?

HTTPS证书作为保障网站数据传输安全的重要工具,成为众多网站运营者的必备选择。然而,面对市场上种类繁多的HTTPS证书,其一年费用究竟是多少,又受哪些因素影响呢? 首先,HTTPS证书通常在PinTrust这样的专业平…...

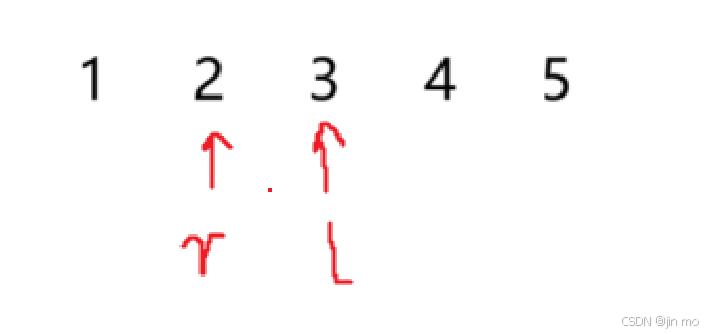

leetcode_69.x的平方根

题目如下 : 看到题 ,我们最原始的想法就是暴力解决: for(long long i 0;i<INT_MAX;i){if(i*ix){return i;}else if((i*i>x)&&((i-1)*(i-1)<x)){return i-1;}}我们直接开始遍历,我们是整数的平方根,所以我们分两…...

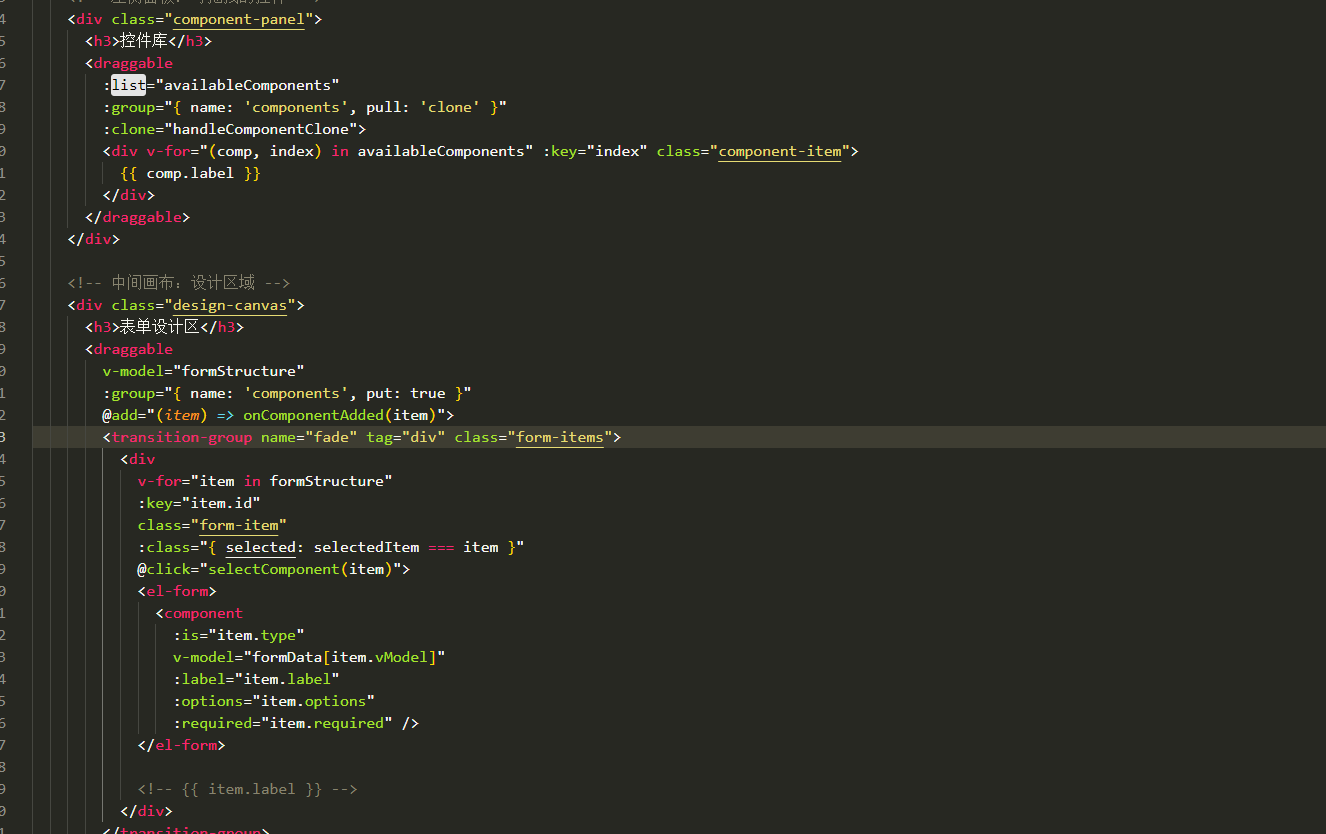

表单设计器拖拽对象时添加属性

背景:因为项目需要。自写设计器。遇到的坑在此记录 使用的拖拽组件时vuedraggable。下面放上局部示例截图。 坑1。draggable标签在拖拽时可以获取到被拖拽的对象属性定义 要使用 :clone, 而不是clone。我想应该是因为draggable标签比较特。另外在使用**:clone时要将…...

安宝特方案丨从依赖经验到数据驱动:AR套件重构特种装备装配与质检全流程

在高压电气装备、军工装备、石油测井仪器装备、计算存储服务器和机柜、核磁医疗装备、大型发动机组等特种装备生产型企业,其产品具有“小批量、多品种、人工装配、价值高”的特点。 生产管理中存在传统SOP文件内容缺失、SOP更新不及、装配严重依赖个人经验、产品装…...

C++ 变量和基本类型

1、变量的声明和定义 1.1、变量声明规定了变量的类型和名字。定义初次之外,还申请存储空间,也可能会为变量赋一个初始值。 如果想声明一个变量而非定义它,就在变量名前添加关键字extern,而且不要显式地初始化变量: e…...

【Go语言基础【6】】字符串格式化说明

文章目录 零、格式化常用场景一、Go 字符串格式化核心概念二、常用格式化占位符1. 整数类型2. 浮点数类型3. 字符串与布尔类型4. 指针与通用类型 三、宽度与精度控制1. 宽度控制2. 精度控制(浮点数/字符串) 零、格式化常用场景 数值转字符串:…...