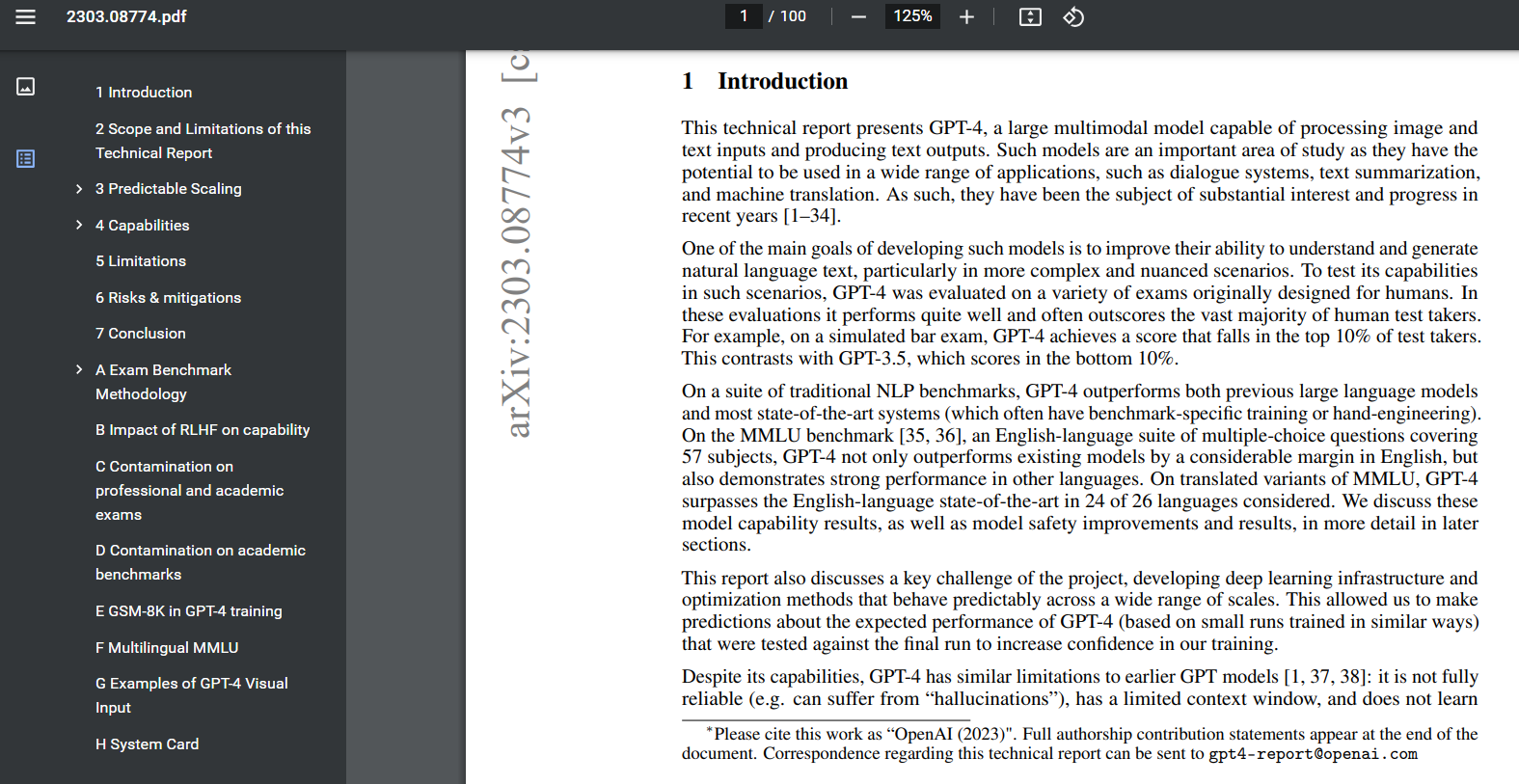

DC LAB8SDC约束四种时序路径分析

DC LAB

- 1.启动DC

- 2.读入设计

- 3. 查看所有违例的约束报告

- 3.1 report_constraint -all_violators (alias rc)

- 3.2 view report_constraint -all_violators -verbose -significant_digits 4 (打印详细报告)

- 4.查看时序报告 report_timing -significant_digits 4

- 5. 约束组合逻辑(adr_i/coff到comb logic到dout)

- 5.1 创建虚拟时钟

- 5.1.1 set_input_delay 用法

- 5.2 创建虚拟时钟vclk后再report_timing

- 5.2.1 组合逻辑约束,clk与vclk logically_exclusive(设置`clk-->comb-->vclk`, `vclk-->comb-->clk`为false)

- 5.2.2 设置`clk与vclk llogically_exclusive`后再去report_timing -group vclk -significant_digits 4

- 5.3 查看clk的timing, report_timing -group clk -significant_digits 4

- 5.3.1 组合逻辑约束,`设置clk--->comb-->clk为false path`

- 5.3.2 设置`clk--->comb-->clk为false path` 后再report_timing -from $in_ports -to [all_outputs]

- 6. 查看clk group timing ,report_timing -group clk

- 6.1 设置`mul_result_reg*/D `(reg2reg)多周期检查setup `set_multicycle_path `

- 6.1.1 设置完setup,多周期再检查reg2reg(`coeff_q_reg_14_ ` to `mul_result_reg_31_`)的setup

- 6.2 检查hold(肯定violation,多周期设置没设置hold,只设置了setup,hold现在在5ns检查太严格了)

- 6.2.1 设置 `mul_result_reg*/D ` (reg2reg)多周期检查hold

- 6.2.2 设置hold多周期后再检查

- 7.report_constraint -all_violators

- 8.四种时序路径总结

- 8.1 in2reg

- 8.2 reg2reg

- 8.3 reg2out

- 8.4 in2out

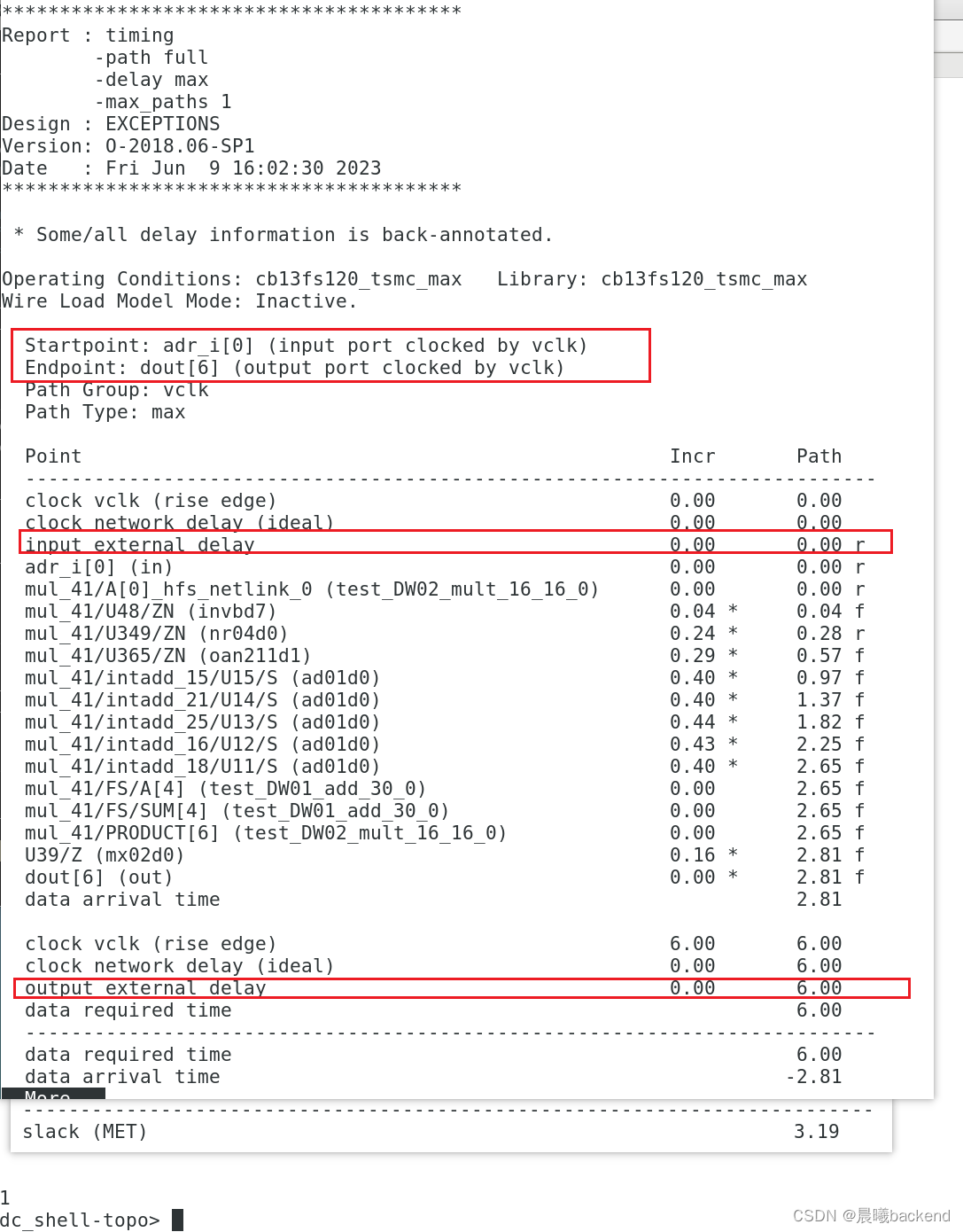

- 8.4.1 in2out`(adr_i[0]-->dout[6]) `demo

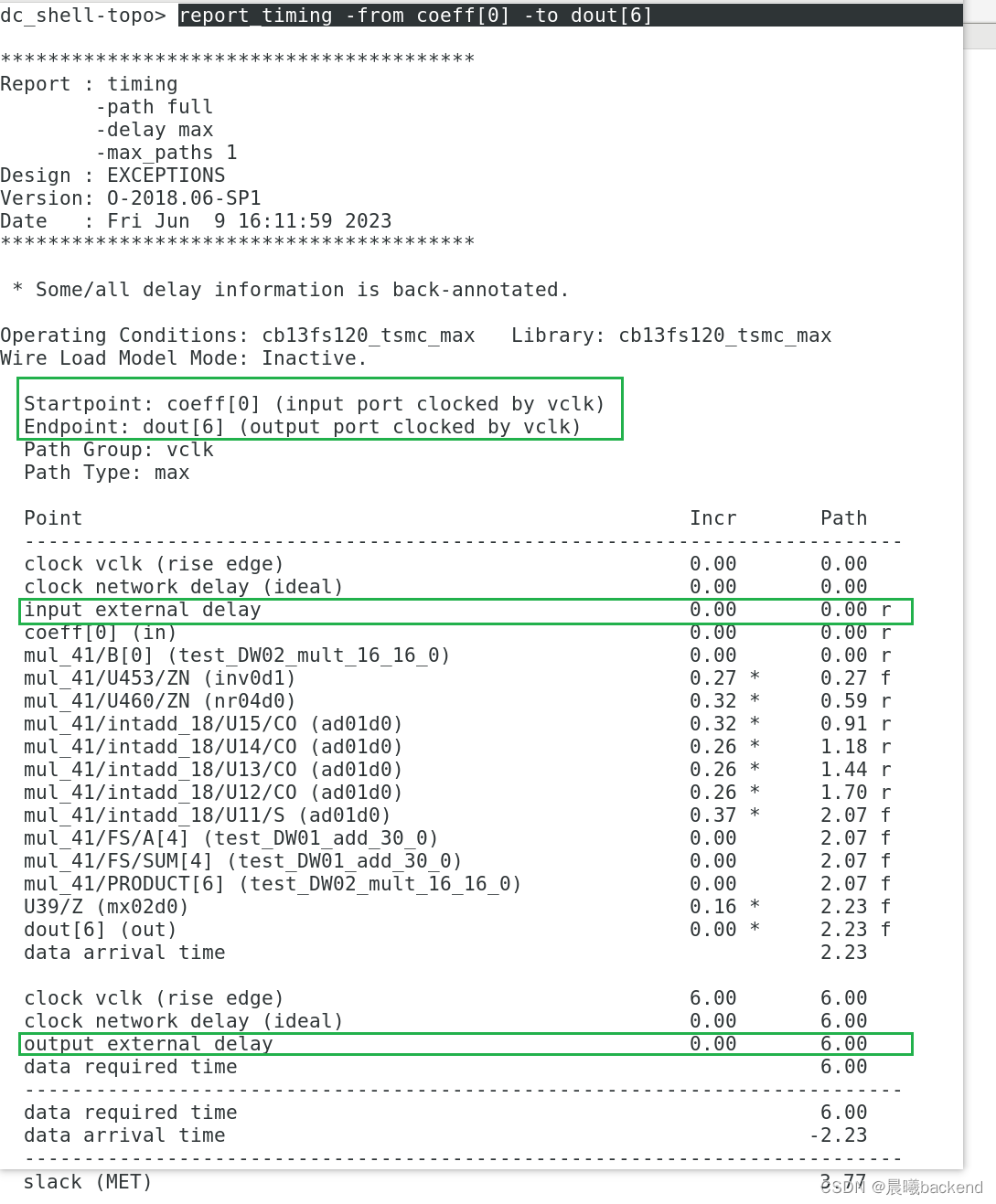

- 8.4.2 in2out`(coeff[5]-->dout[6]) `demo

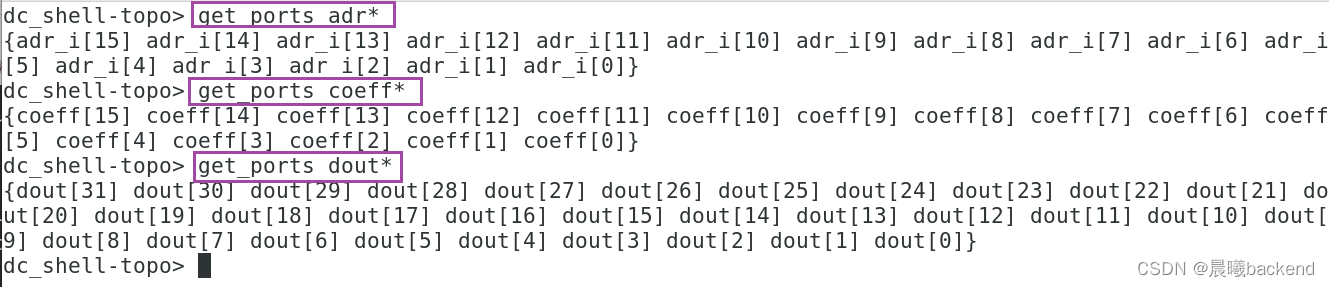

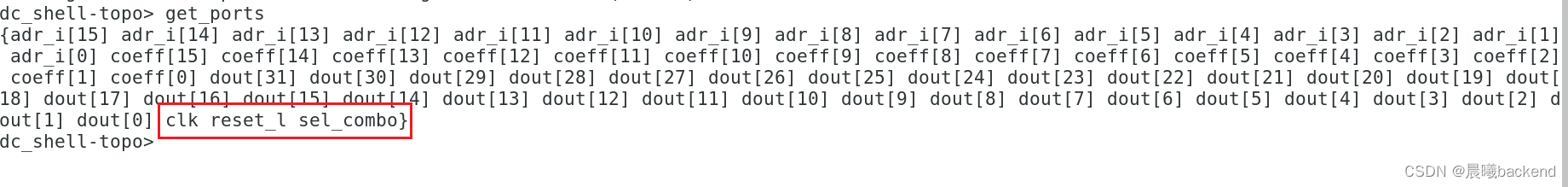

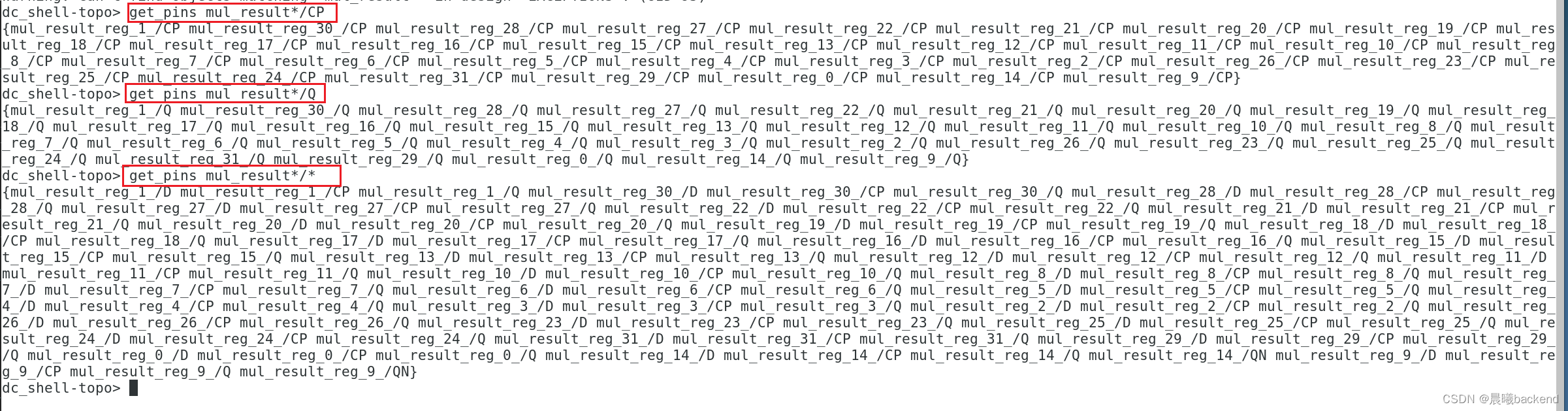

- 9.打印所有port、cells、pins

- get_ports

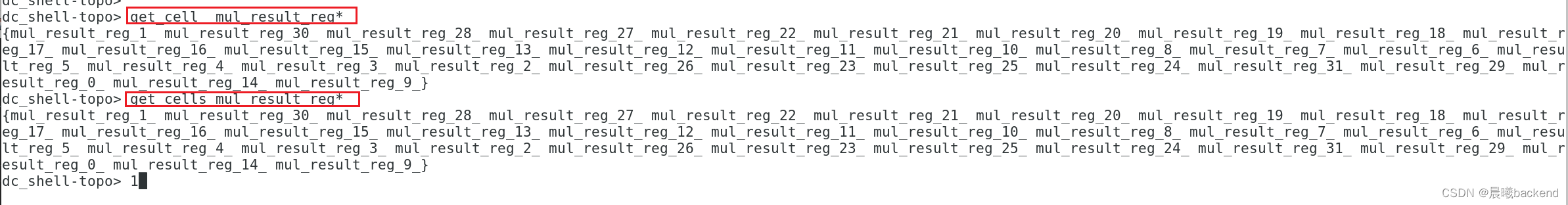

- get_cells

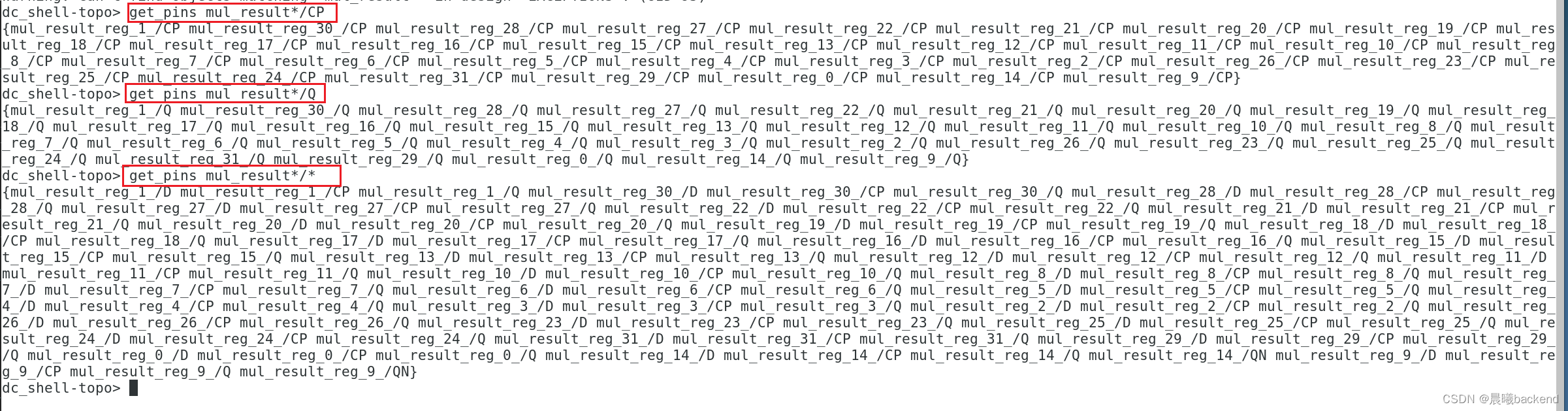

- get_pins

1.启动DC

dc_shell-t -64bit -topo

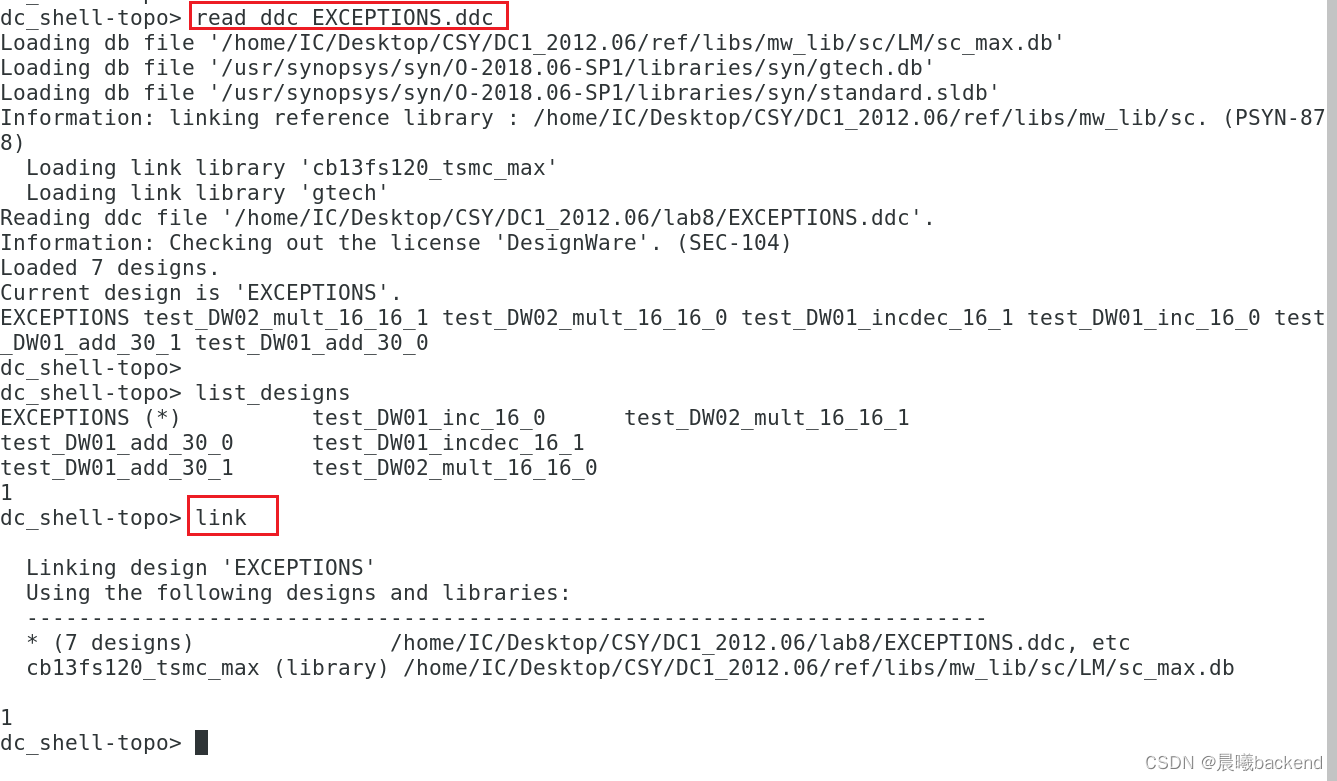

2.读入设计

read_ddc EXCEPTIONS.ddc

current_design EXCEPTIONS

link

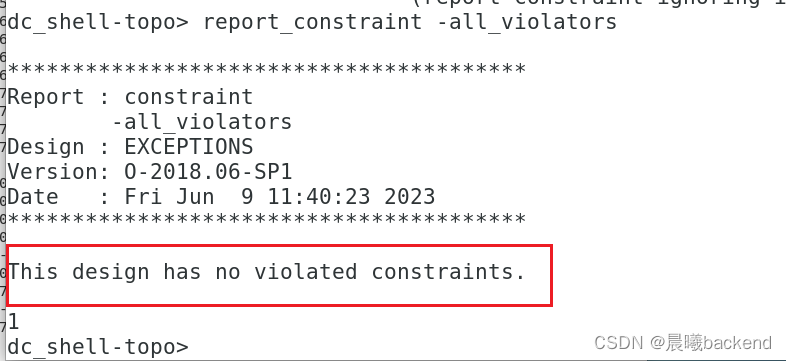

3. 查看所有违例的约束报告

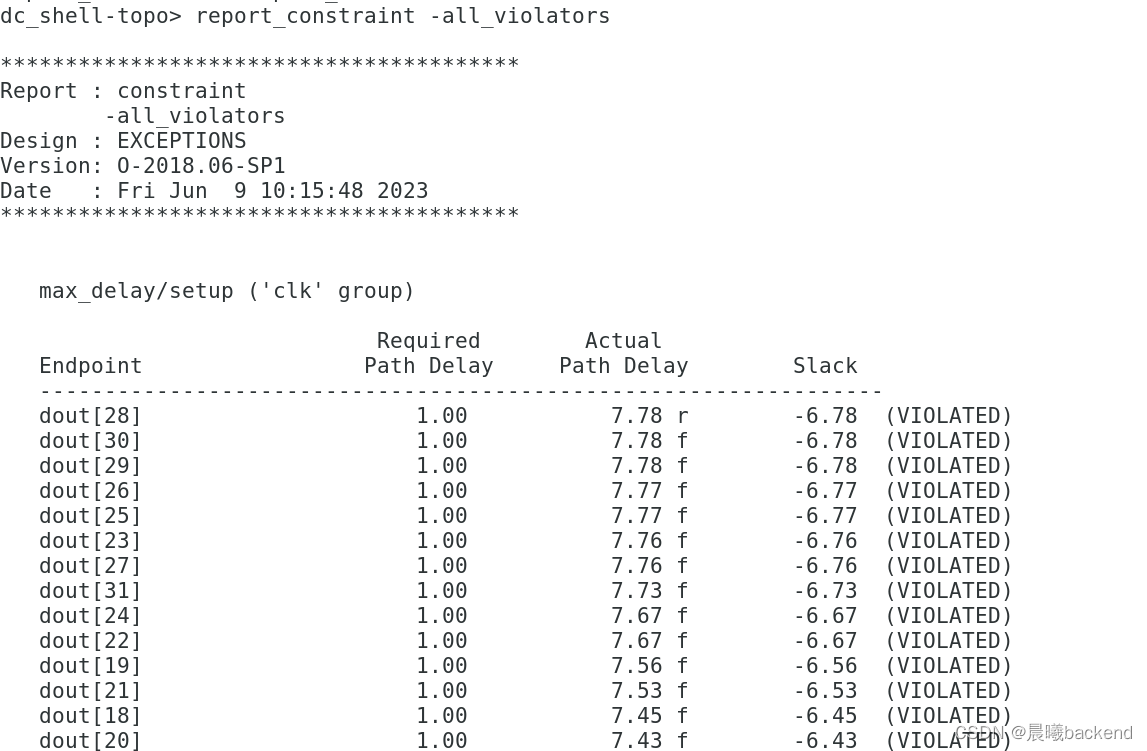

3.1 report_constraint -all_violators (alias rc)

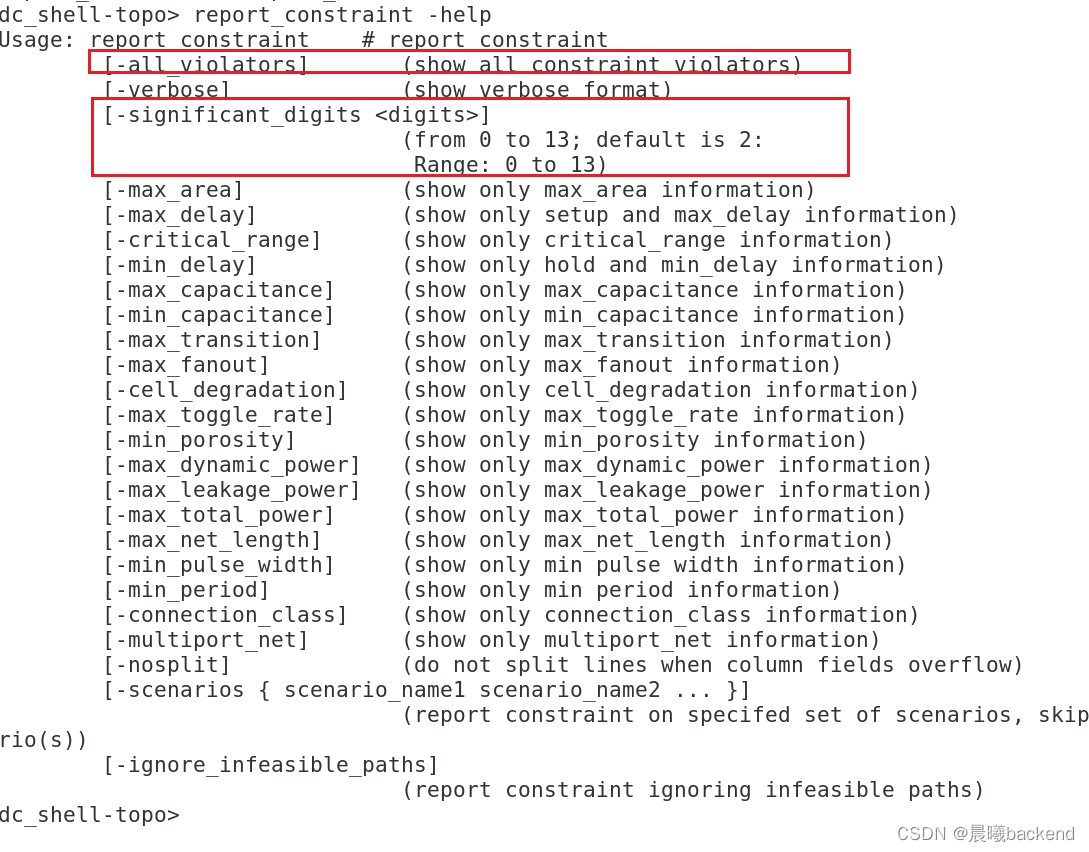

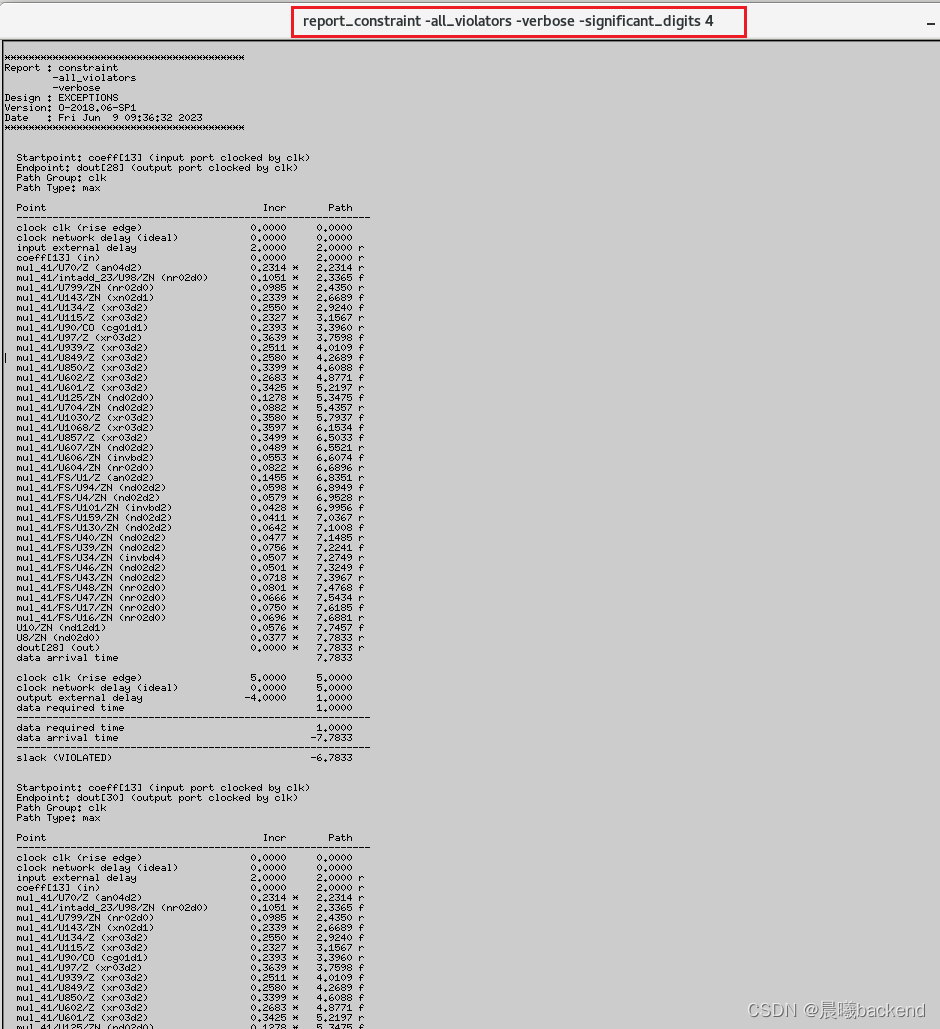

3.2 view report_constraint -all_violators -verbose -significant_digits 4 (打印详细报告)

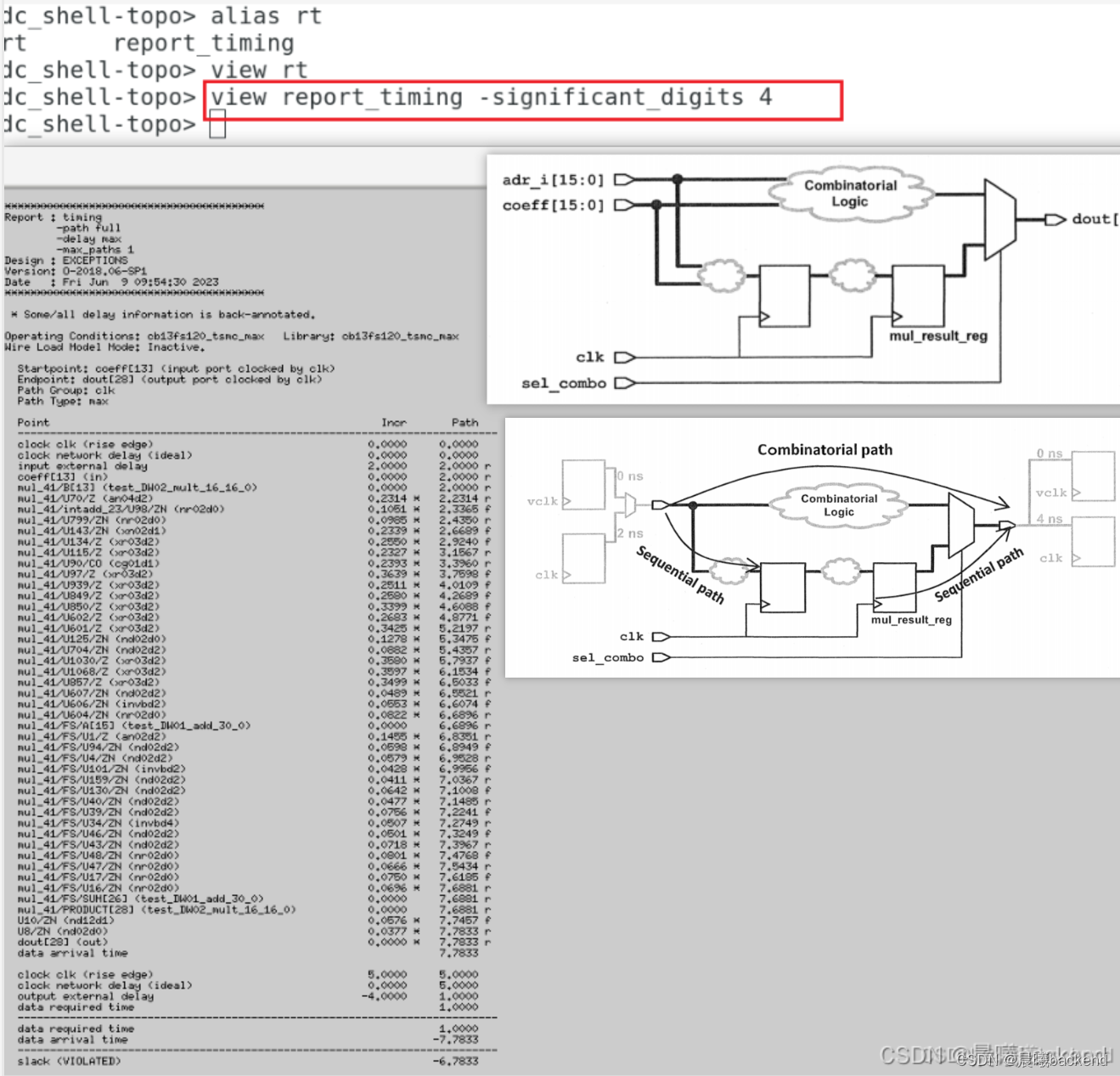

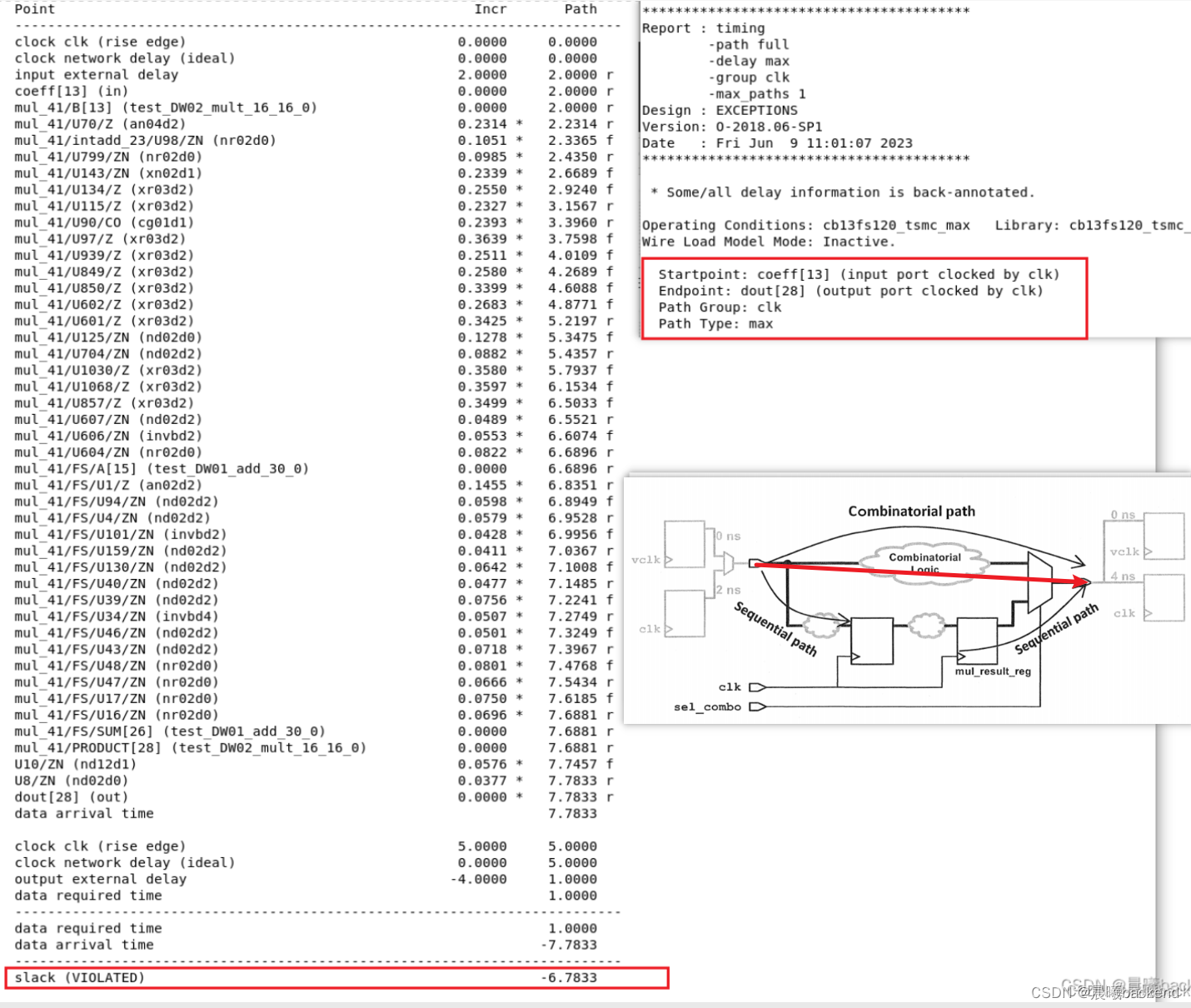

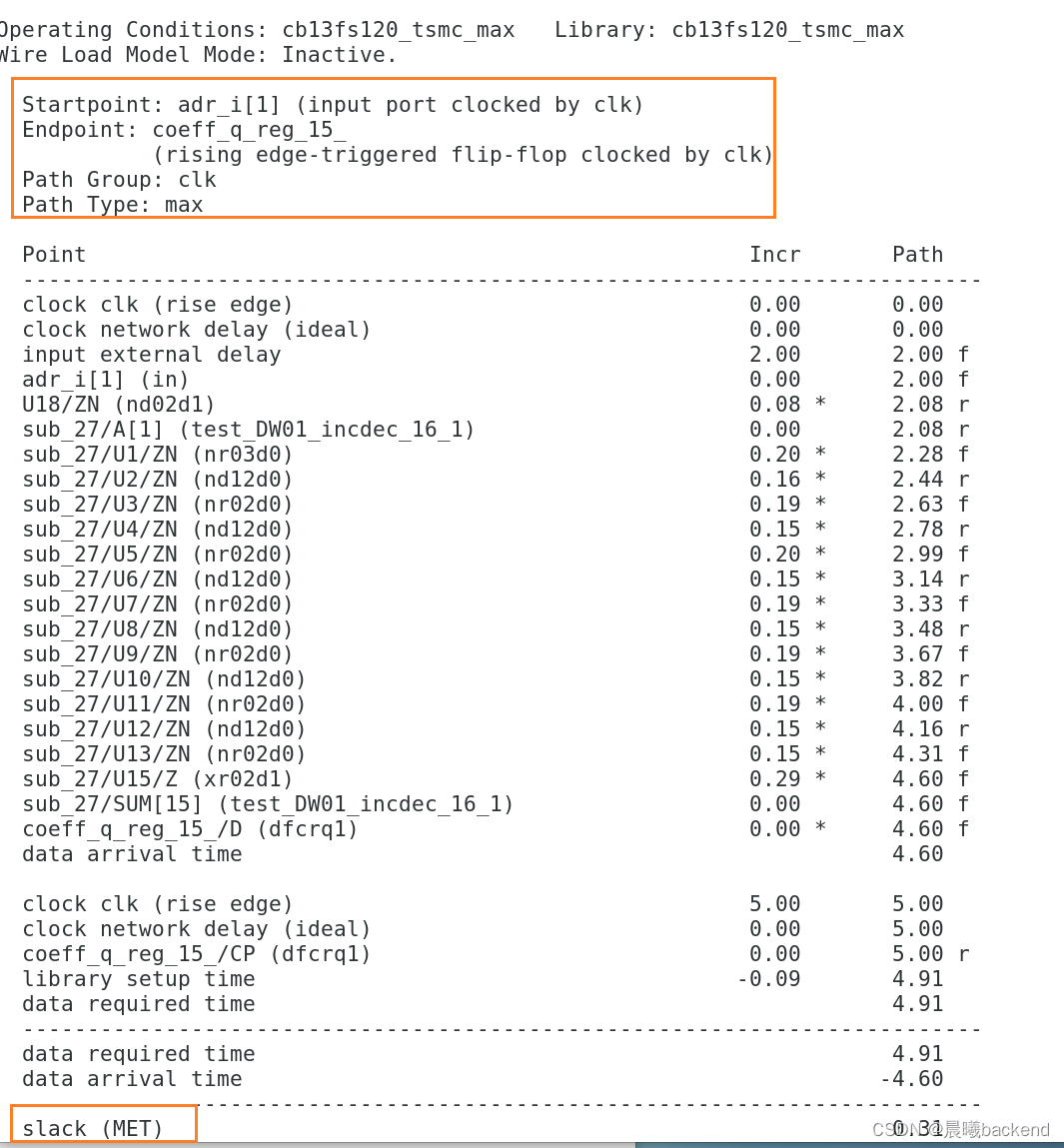

4.查看时序报告 report_timing -significant_digits 4

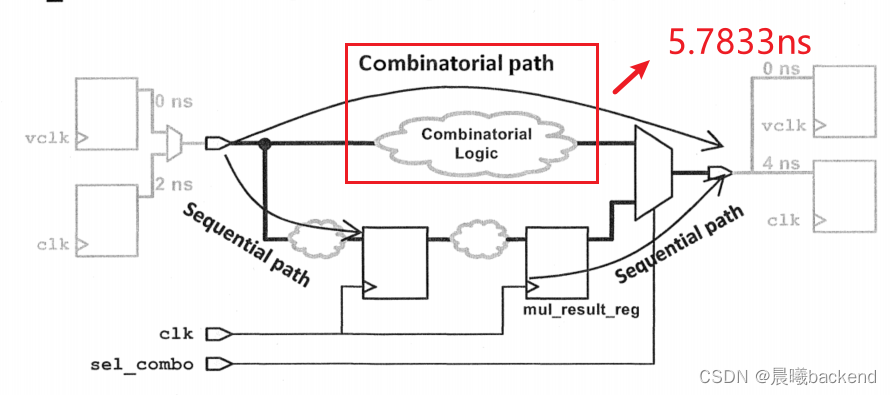

- 组合逻辑延时是7.7833-2=5.7833

- 对于adr_i/coff到comb logic到dout,

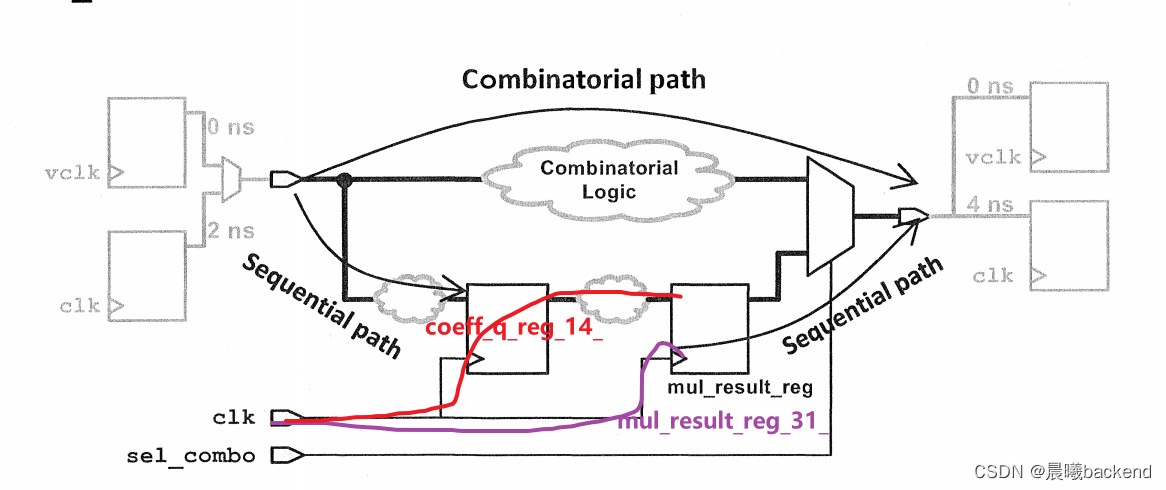

(in2out,应该定义虚拟时钟vclk),将clk-->comb-->clk,clk-->comb-->vclk,vclk-->comb-->clk,这三条设置false - 上图是adr_i/coff到comb logic到dout时序路径,有vio(clk–>input delay 2ns -->coff --> comb logic 5.7833ns --> dout) 这条路径应设置false path

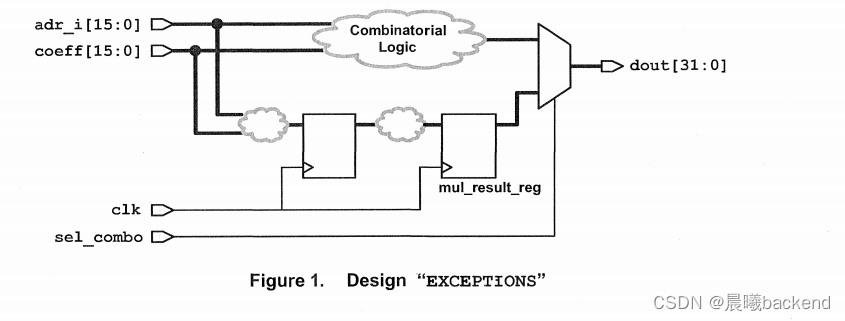

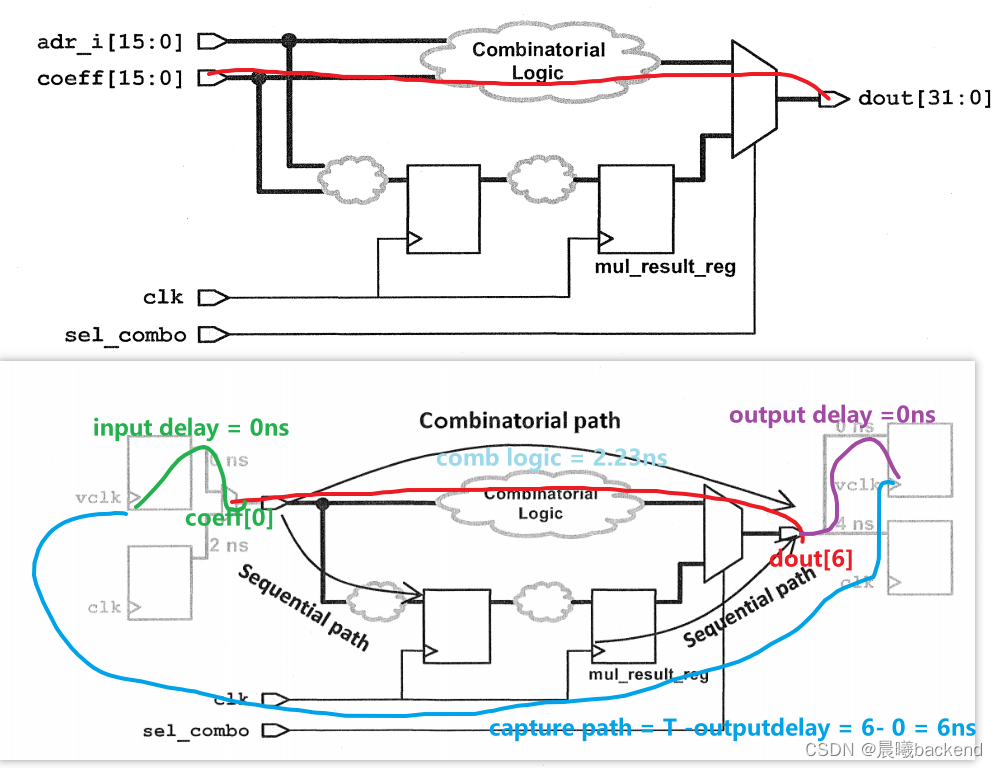

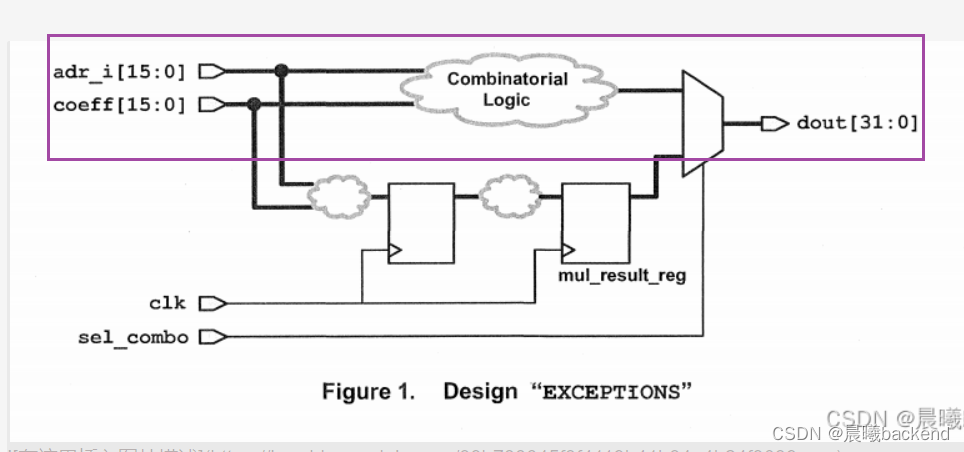

5. 约束组合逻辑(adr_i/coff到comb logic到dout)

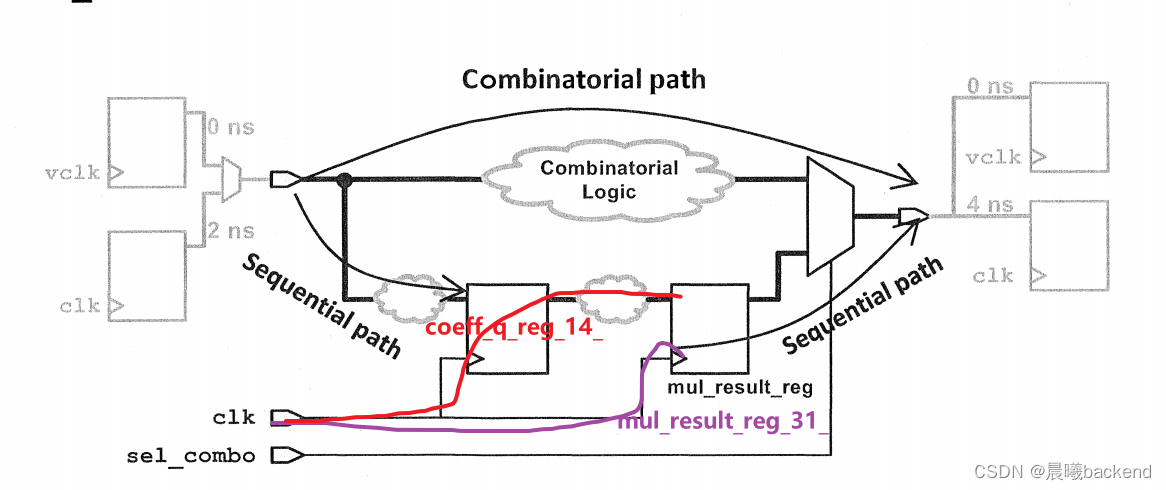

- To accomplish this,the combinatorial paths will be constrained using a new virtual clock which you will call vclk.

- The sequential paths are already constrained using the 5ns design clock clk,and input and output delays of 2ns and 4ns,respectively.

- The following schematic illustrates this concept (note that the two input ports, adr_ i and coeff,are collapsed into one port here to simplify the schematic):

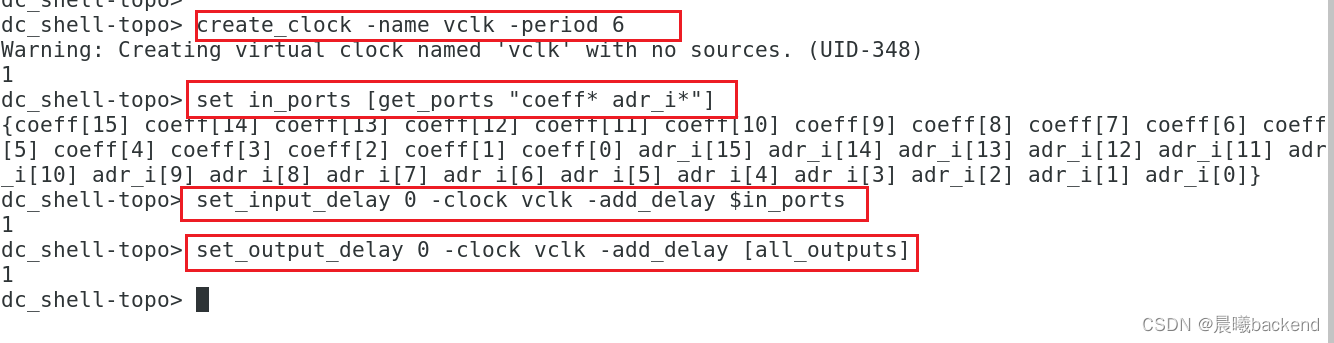

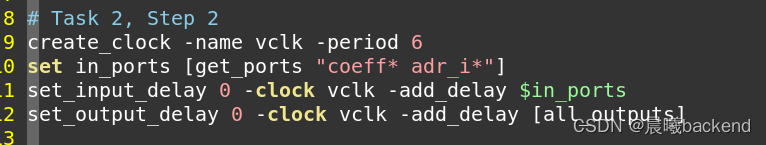

5.1 创建虚拟时钟

create_clock -name vclk -period 6

set in_ports [get_ports "coeff* adr_i*"]

set_input_delay 0 -clock vclk -add_delay $in_ports

set_output_delay 0 -clock vclk -add_delay [all_outputs]

5.1.1 set_input_delay 用法

dc_shell-topo> set_input_delay -help

Usage: set_input_delay # set input_delay[-clock clock_name] (relative clock)[-clock_fall] (delay is relative to falling edge of clock)[-level_sensitive] (delay is from level-sensitive latch)[-rise] (specifies rising delay)[-fall] (specifies falling delay)[-max] (specifies maximum delay)[-min] (specifies minimum delay)[-add_delay] (don't remove existing input delay)[-network_latency_included](specifies that clock_network_latency is included)[-source_latency_included](specifies that clock_source_latency is included)[-reference_pin pin_list](list of pins)delay_value (path delay)port_pin_list (list of ports and/or pins)

5.2 创建虚拟时钟vclk后再report_timing

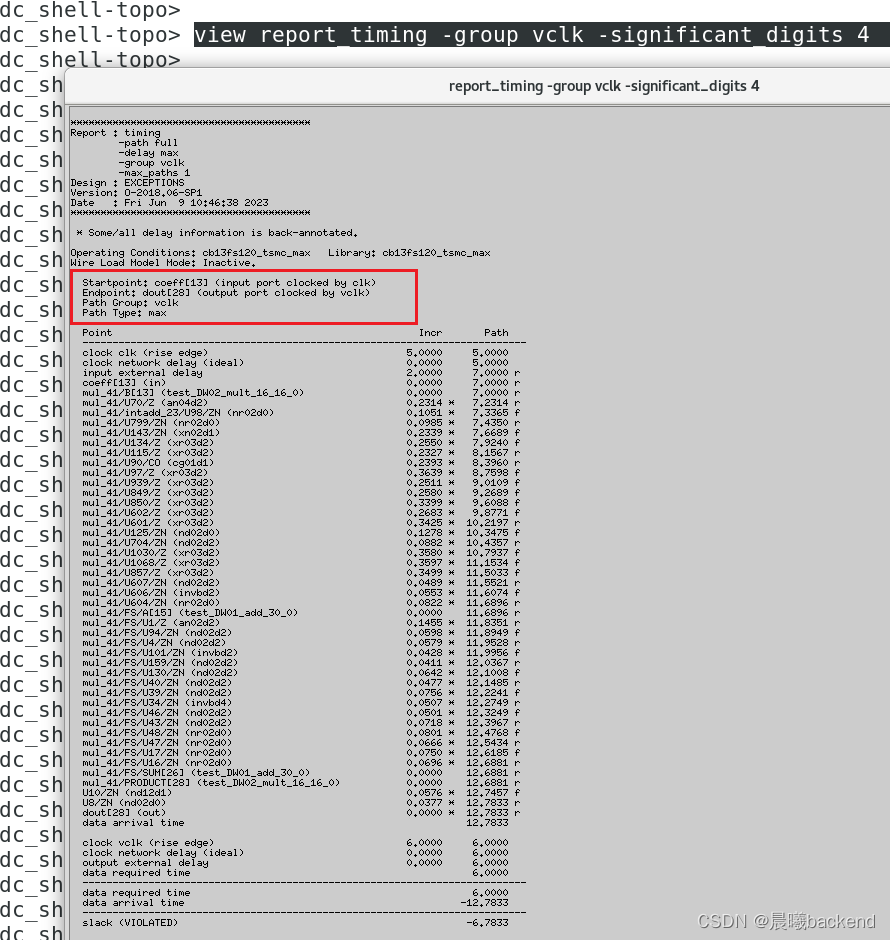

view report_timing -group vclk -significant_digits 4

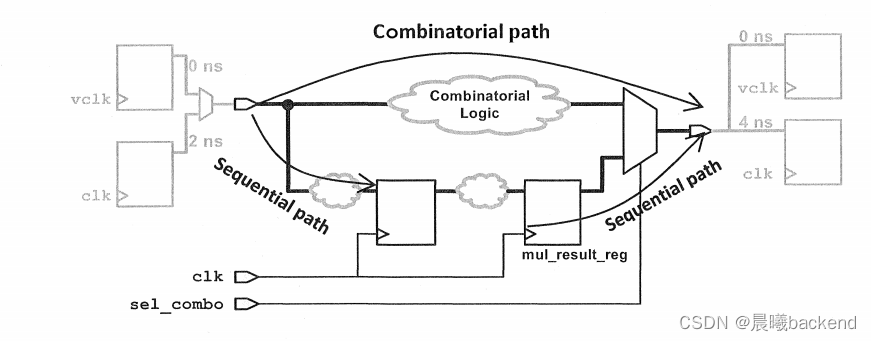

- 组合逻辑的路径应该只有vclk约束,设置

clk-->comb-->clk,clk-->comb-->vclk,vclk-->comb-->clk为false - The launch clock is vclk and the capture clock is vclk . This is not correct!

- The combinatorial paths should be constrained only by vclk . The two clocks should not interact.

5.2.1 组合逻辑约束,clk与vclk logically_exclusive(设置clk-->comb-->vclk, vclk-->comb-->clk为false)

- 对于

clk-->comb-->clk只有手动设置false了 (5.3.1)

#两种时钟,四种组合,约束后只能从clk到clk或者vclk到vclk

#

set_clock_group -name false_grp1 -logically_exclusive -group clk -group vclk# Altenatively:

#

# set_false_path -from [get_clocks clk] -to [get_clocks vclk]

# set_false_path -from [get_clocks vclk] -to [get_clocks clk]

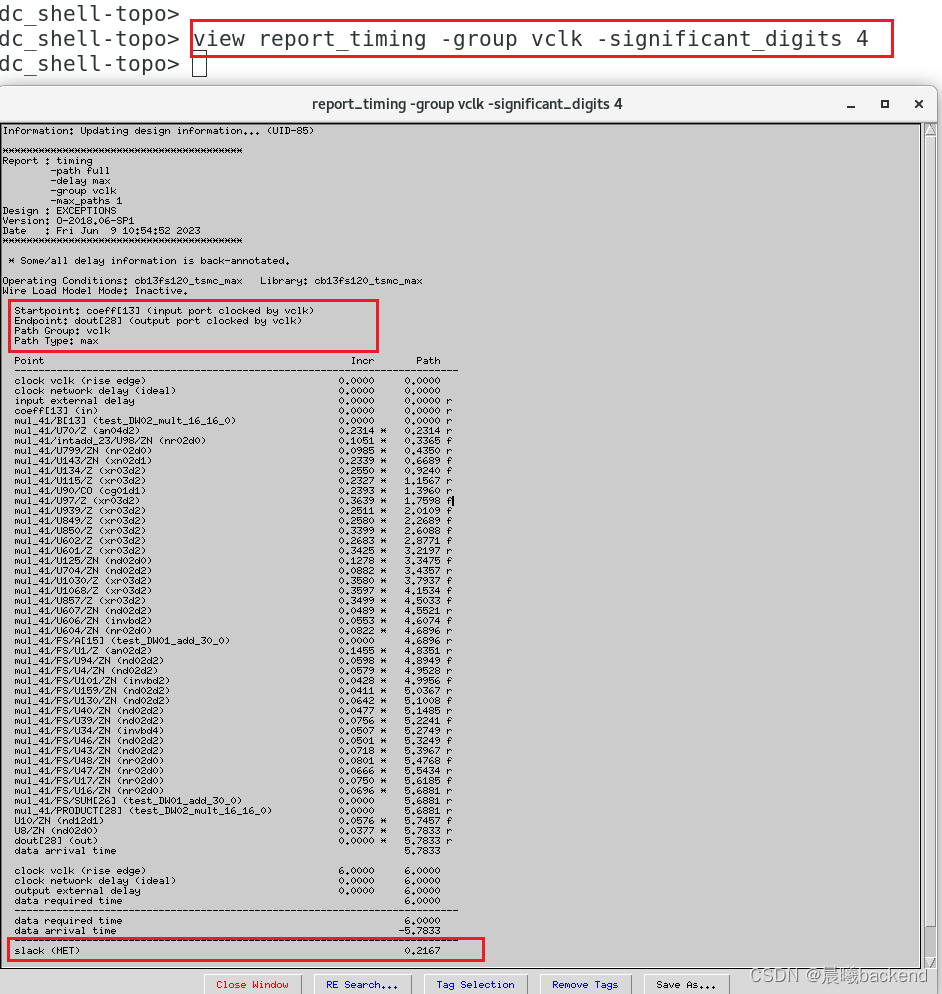

5.2.2 设置clk与vclk llogically_exclusive后再去report_timing -group vclk -significant_digits 4

- 组合逻辑延时 5.7833ns

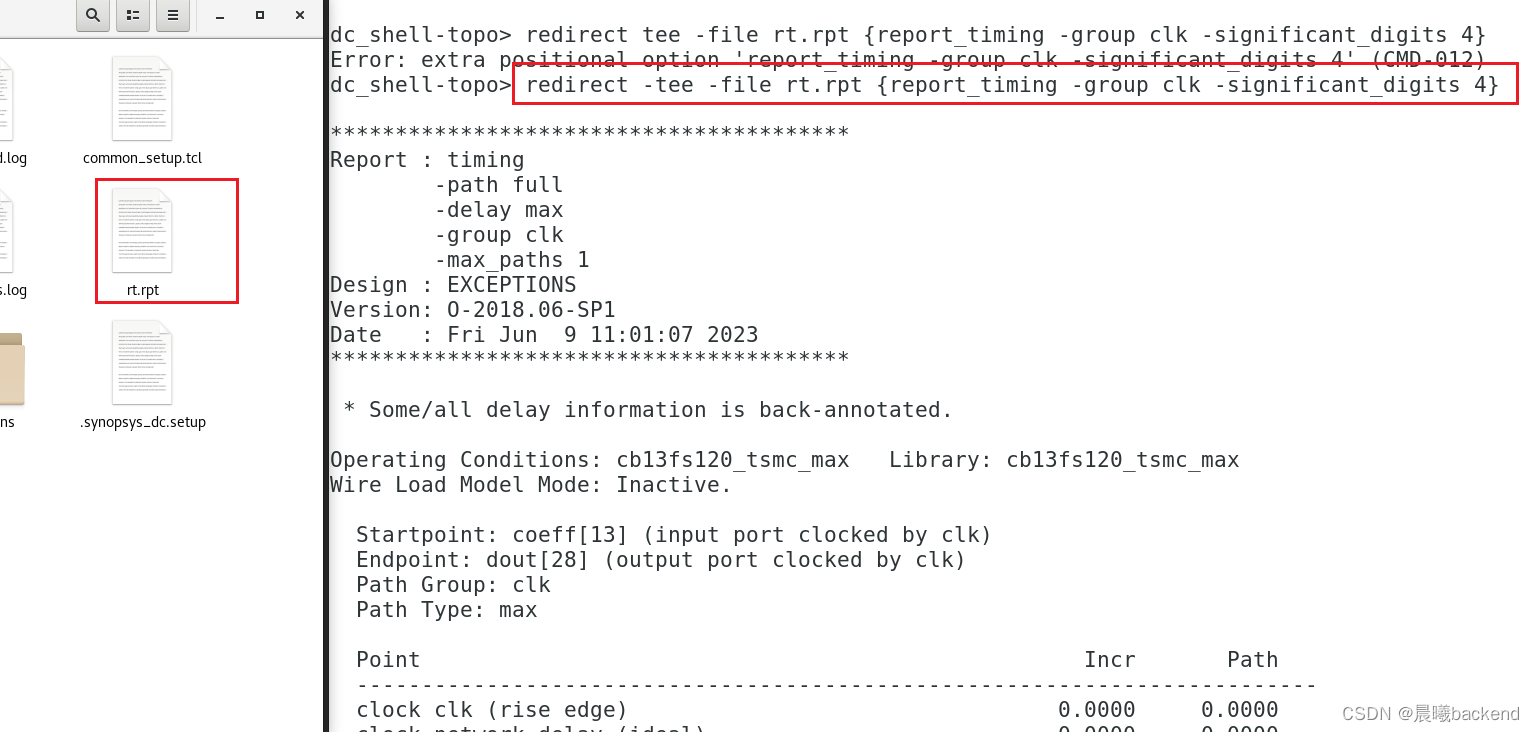

5.3 查看clk的timing, report_timing -group clk -significant_digits 4

- 这里不会显示

vclk-->clk,因为前面(5.2.1)设置了logically exclusive - 只会显示

clk-->clk

- 上图是addi/coff到comb到dout的时序路径,有vio(clk–>input delay 2ns -->coff --> comb logic 5.7833ns --> dout) 这条路径设置false path ,

- 这条路径用虚拟时钟vclk检查

- 前面5.2.1虽然设置了logic exclusive(

clk-->comb-->vclk,vclk-->comb-->clk为false),但是clk—>comb–>clk还是得手动去 false

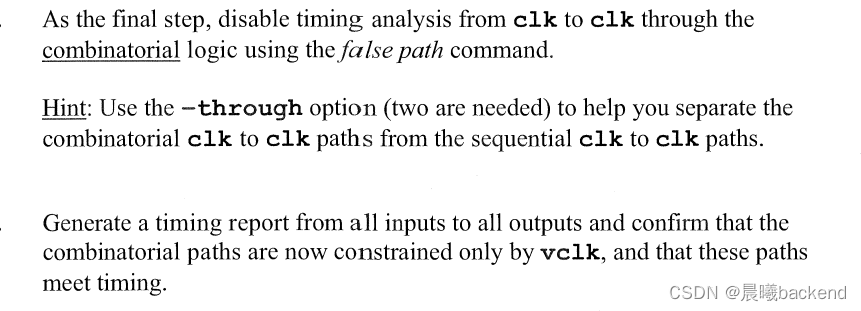

5.3.1 组合逻辑约束,设置clk--->comb-->clk为false path

set_false_path -from [get_clocks clk] \-through $in_ports \-through [all_outputs] -to [get_clocks clk]

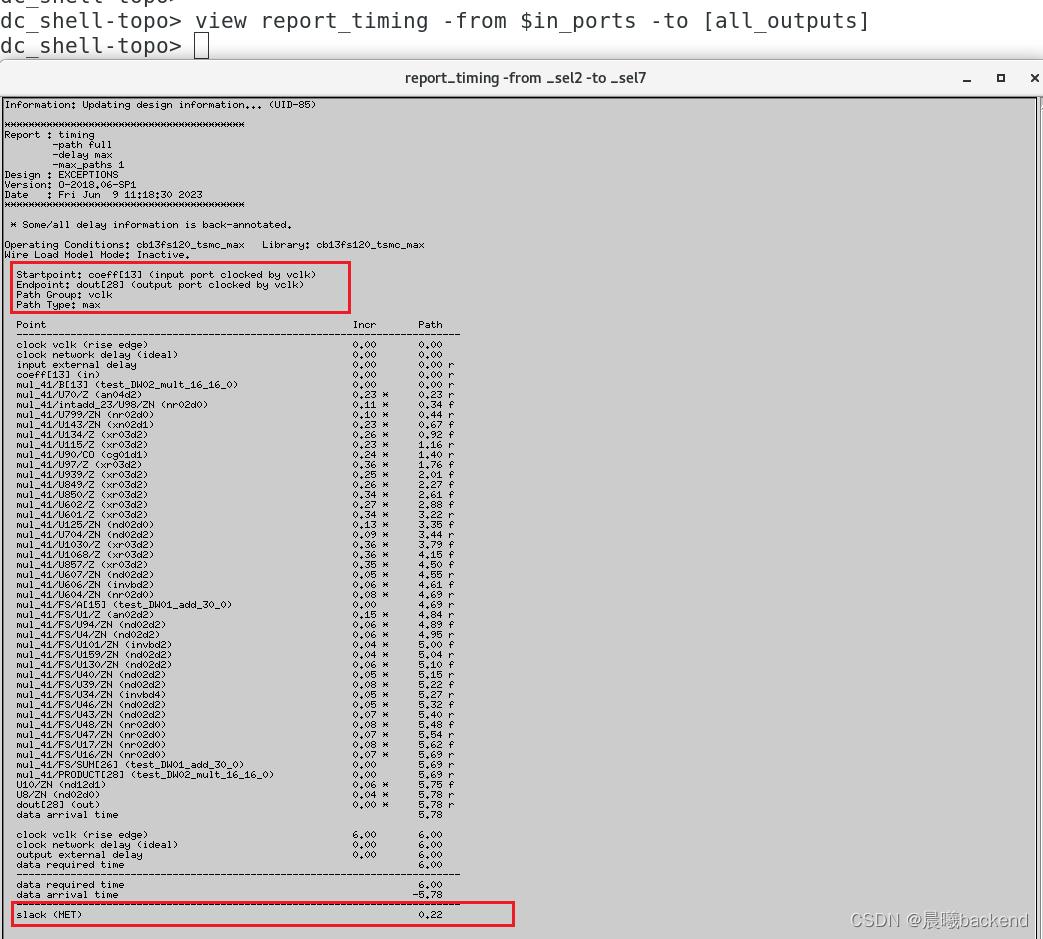

5.3.2 设置clk--->comb-->clk为false path 后再report_timing -from $in_ports -to [all_outputs]

- 由于设置

clk-->comb-->clk,clk-->comb-->vclk,vclk-->comb-->clk为false,故只会显示vclk–>vcomb–>clk这条时序路径

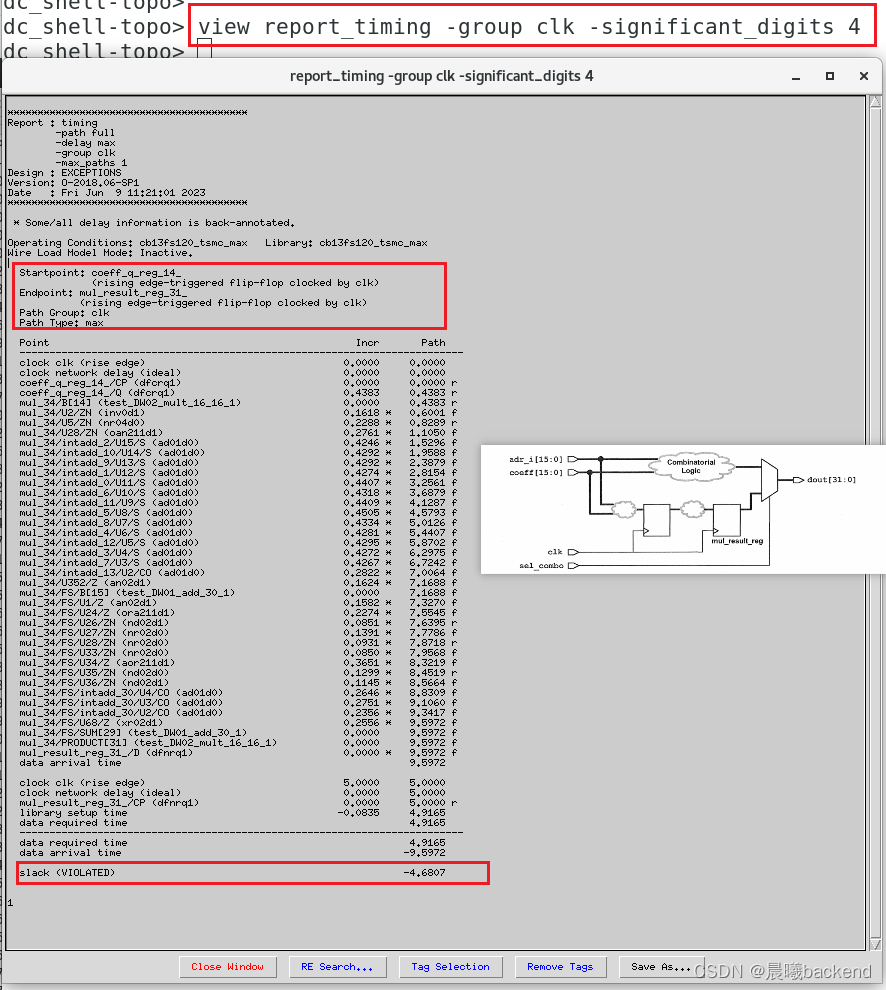

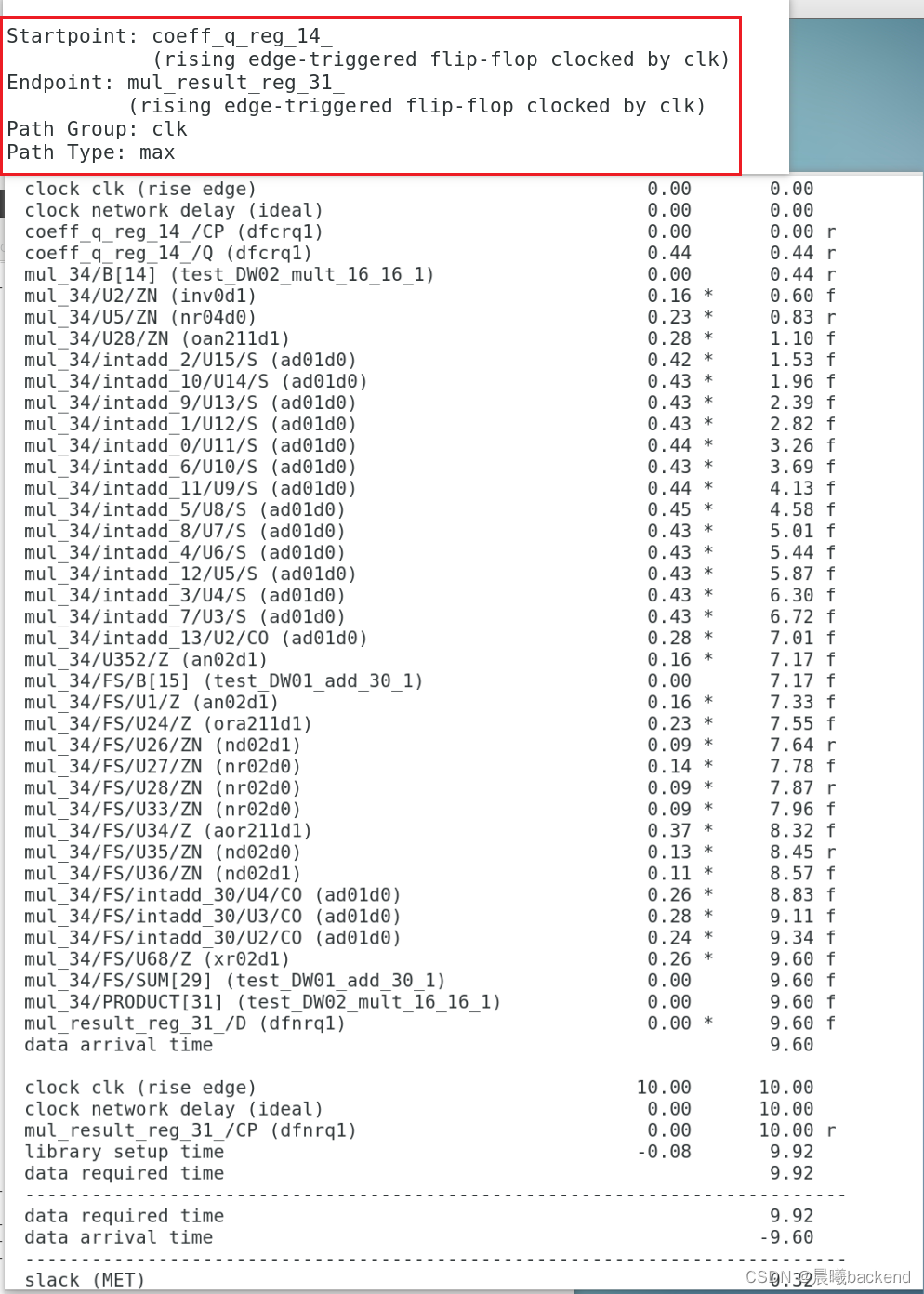

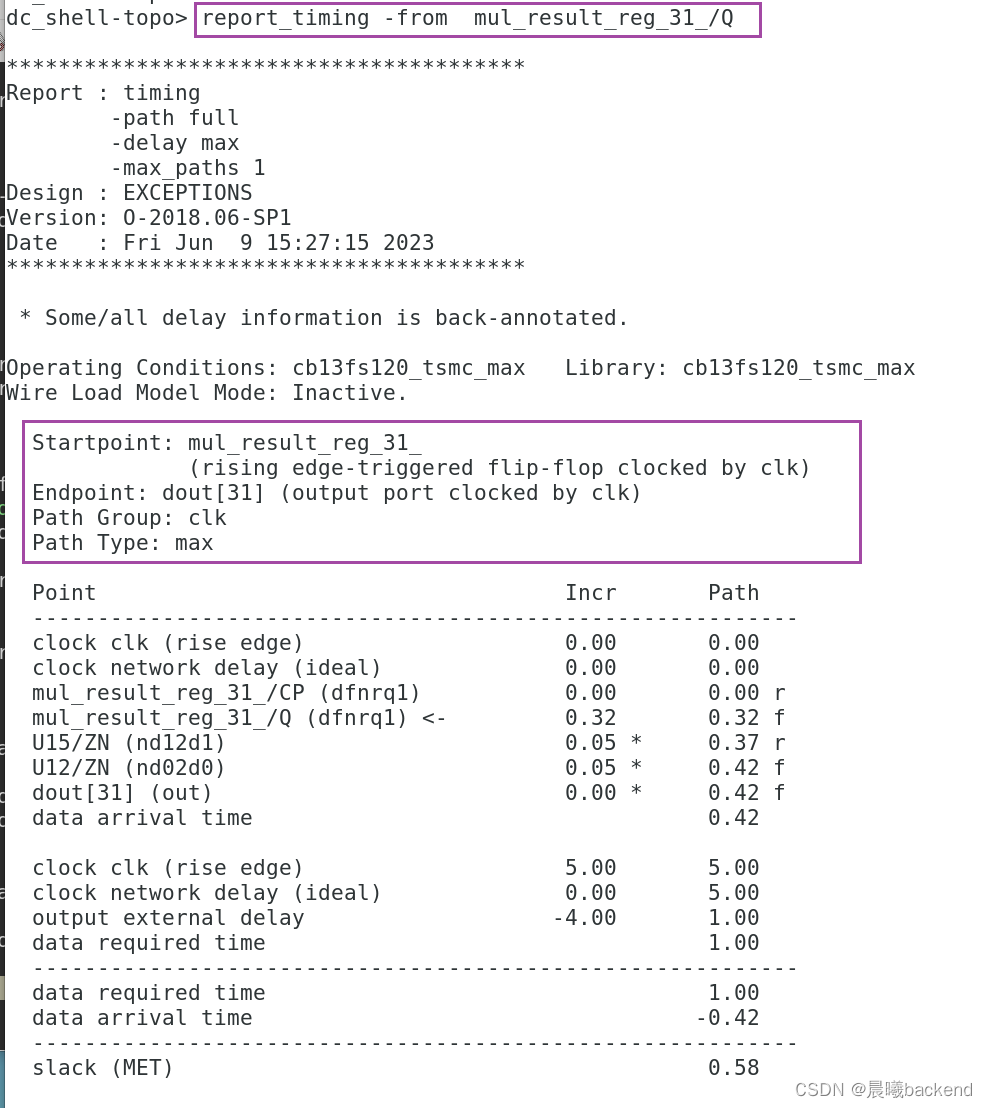

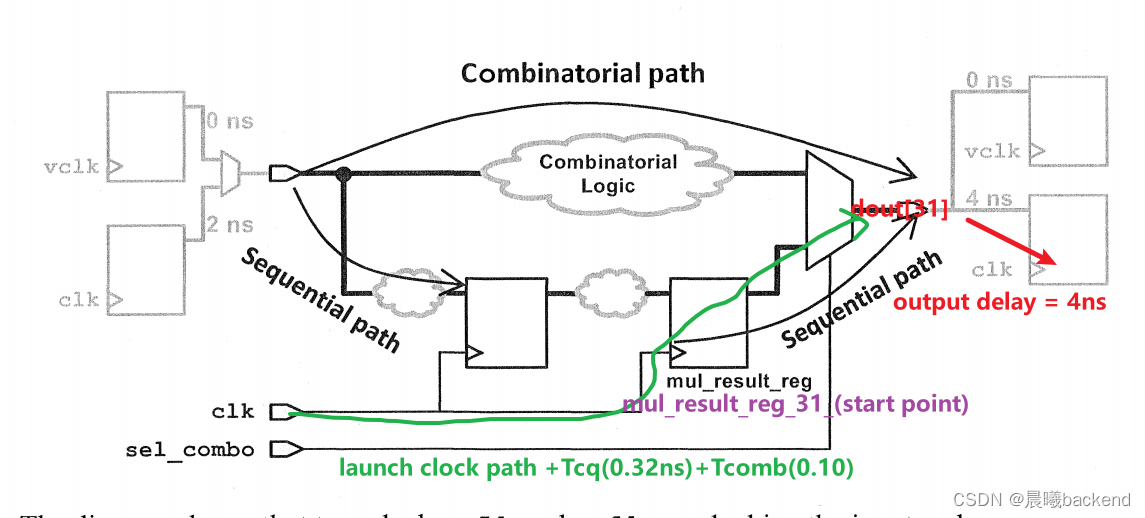

6. 查看clk group timing ,report_timing -group clk

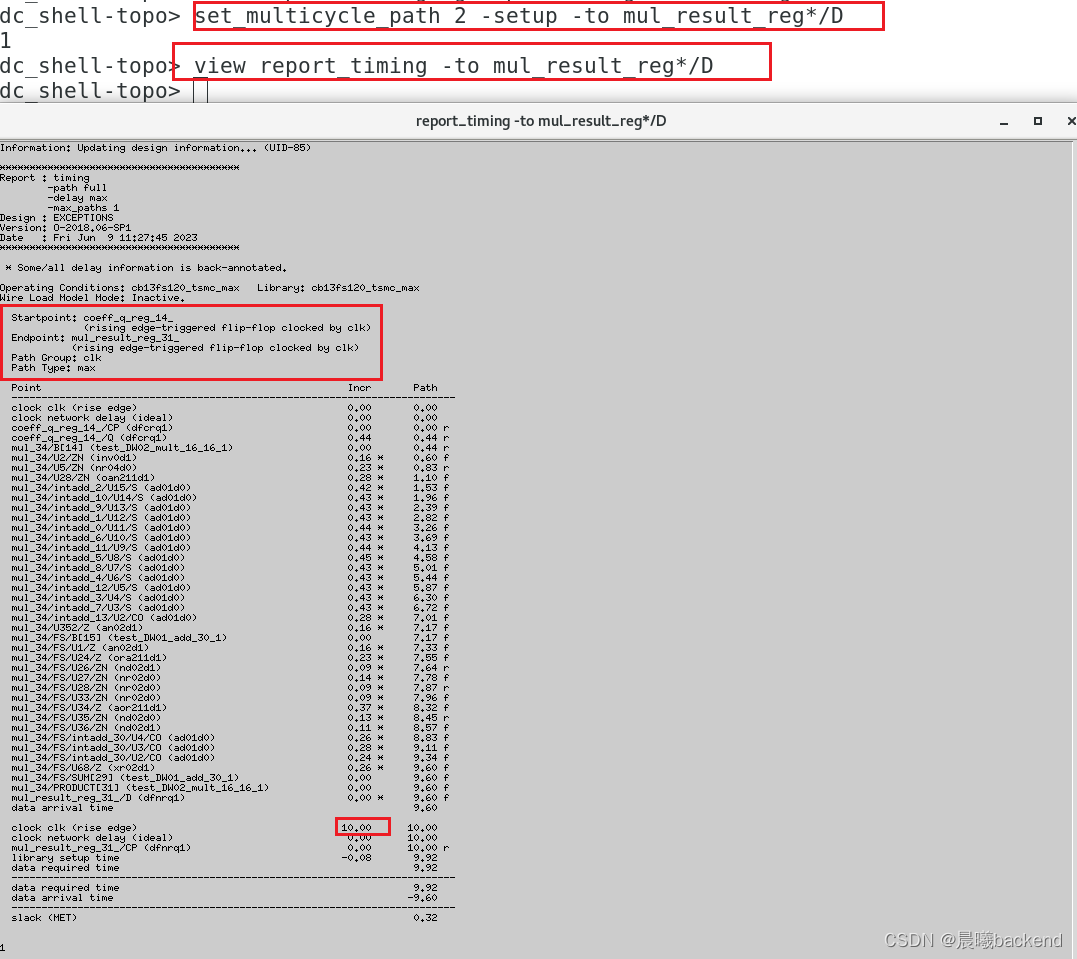

- 从下图可以看出reg2reg 中间组合逻辑延时为9.1589ns,Tcq=0.4383

- 组合逻辑介于一个周期和两个周期之间,所以设置multicycle path(setup设置N,hold则对应N-1)

两个寄存器间的Tcq+Tcomb = 9.5943,单周期检查太严格,故设置多周期检查,setup在第二个周期在检查

6.1 设置mul_result_reg*/D (reg2reg)多周期检查setup set_multicycle_path

##若setup设置N,hold 对应设置为N-1

set_multicycle_path 2 -setup -to mul_result_reg*/D

6.1.1 设置完setup,多周期再检查reg2reg(coeff_q_reg_14_ to mul_result_reg_31_)的setup

- 由于只设置了setup,所以这里检查setup的 comb max delay是没有问题的

- 但是检查hold,就过于严苛了

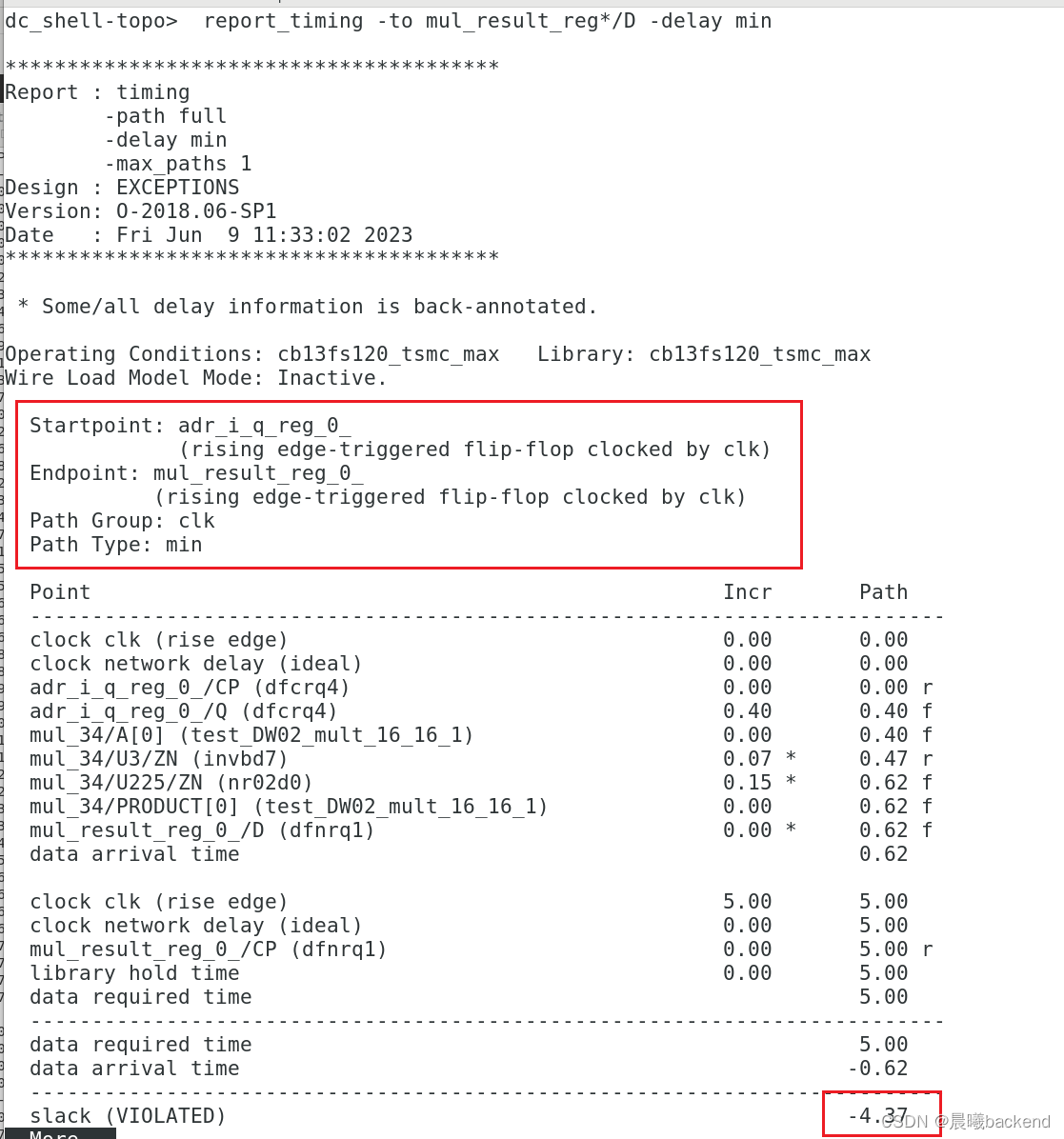

6.2 检查hold(肯定violation,多周期设置没设置hold,只设置了setup,hold现在在5ns检查太严格了)

6.2.1 设置 mul_result_reg*/D (reg2reg)多周期检查hold

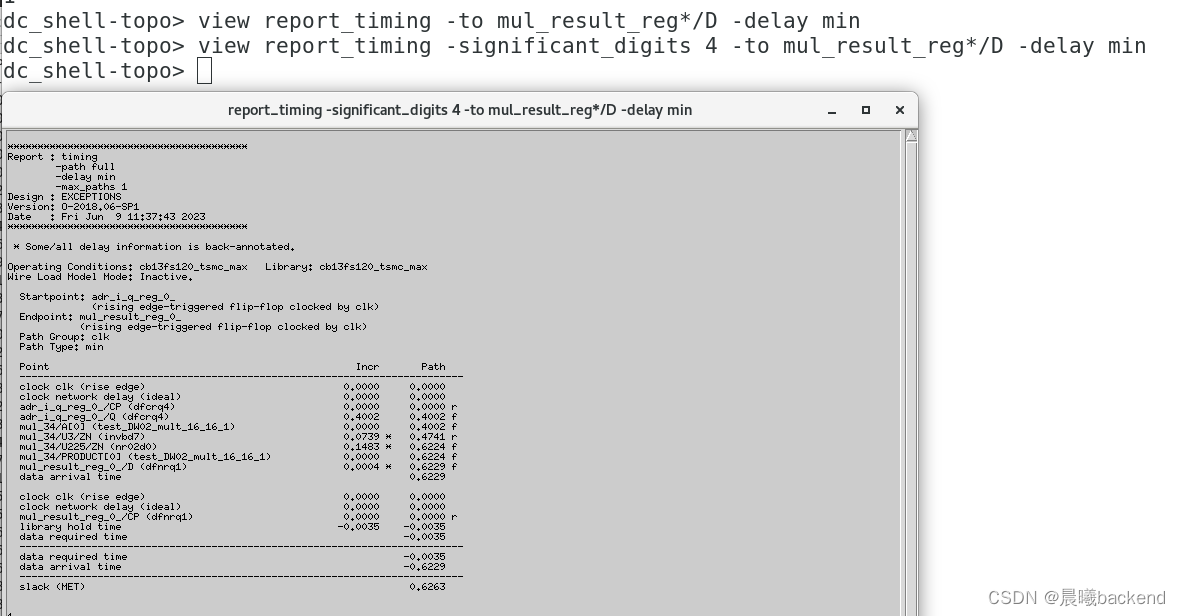

set_multicycle_path 1 -hold -t o mul_result_reg*/D

6.2.2 设置hold多周期后再检查

report_timing -significant_digits 4 -to mul_result_reg*/D -delay min

7.report_constraint -all_violators

- 所有timing vio都已经清除完毕了

8.四种时序路径总结

8.1 in2reg

report_timing -group clk

[-add_delay] (don't remove existing input delay)

8.2 reg2reg

- 这里设置了

set_multicycle_path 2 -setup -to mul_result_reg*/D

8.3 reg2out

8.4 in2out

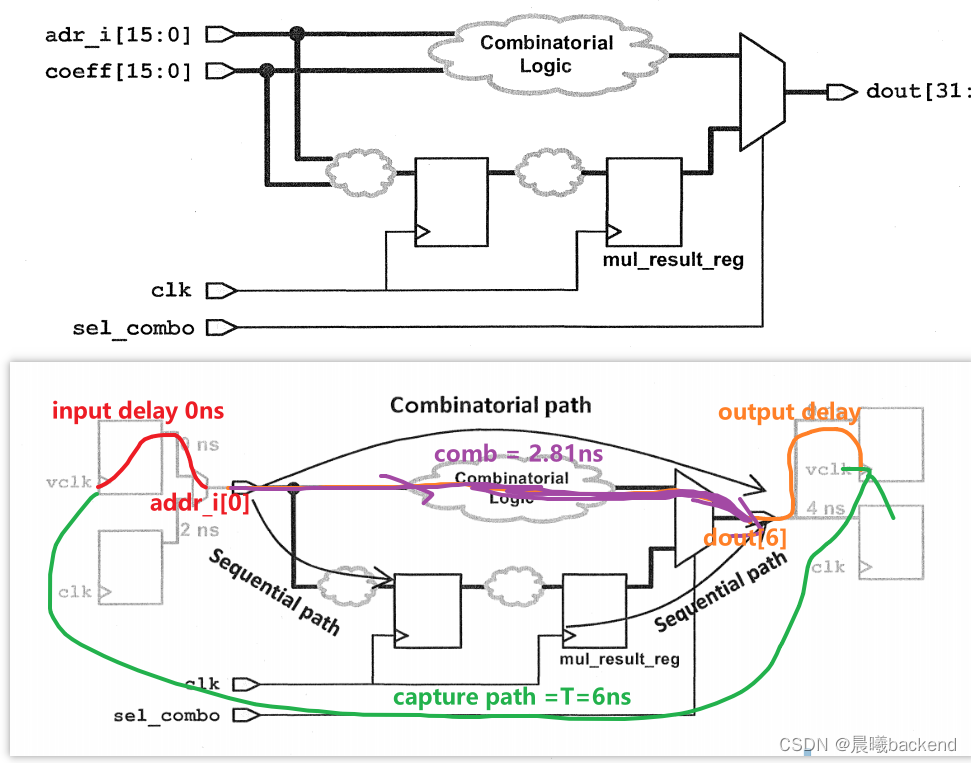

8.4.1 in2out(adr_i[0]-->dout[6]) demo

report_timing -from adr_* -to dout[6]

report_timing -from adr_* -to dout*

8.4.2 in2out(coeff[5]-->dout[6]) demo

report_timing -from coeff* -to dout[6]

report_timing -from coeff[0] -to dout[6]

9.打印所有port、cells、pins

get_ports

get_cells

get_pins

相关文章:

DC LAB8SDC约束四种时序路径分析

DC LAB 1.启动DC2.读入设计3. 查看所有违例的约束报告3.1 report_constraint -all_violators (alias rc)3.2 view report_constraint -all_violators -verbose -significant_digits 4 (打印详细报告) 4.查看时序报告 report_timing -significant_digits 45. 约束组合逻辑(adr_i…...

学生考试作弊检测系统 yolov8

学生考试作弊检测系统采用yolov8网络模型人工智能技术,学生考试作弊检测系统过在考场中安装监控设备,对学生的作弊行为进行实时监测。当学生出现作弊行为时,学生考试作弊检测系统将自动识别并记录信息。YOLOv8 算法的核心特性和改动可以归结为…...

【基于容器的部署、扩展和管理】 3.2 基于容器的应用程序部署和升级

往期回顾: 第一章:【云原生概念和技术】 第二章:【容器化应用程序设计和开发】 第三章:【3.1 容器编排系统和Kubernetes集群的构建】 3.2 基于容器的应用程序部署和升级 3.2 基于容器的应用程序部署和升级 3.2 基于容器的应用程…...

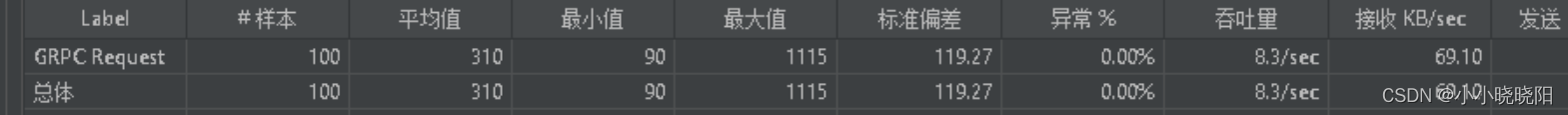

Jmeter 实现 grpc服务 压测

一、Jmeter安装与配置 网上有很多安装与配置文章,在此不做赘述 二、Jmeter gRPC Request 插件安装 插件下载地址:JMeter Plugins :: JMeter-Plugins.org 将下载文件解压后放到Jmeter安装目录下 /lib/ext 然后在终端输入Jmeter即可打开 Jmeter GUI界面…...

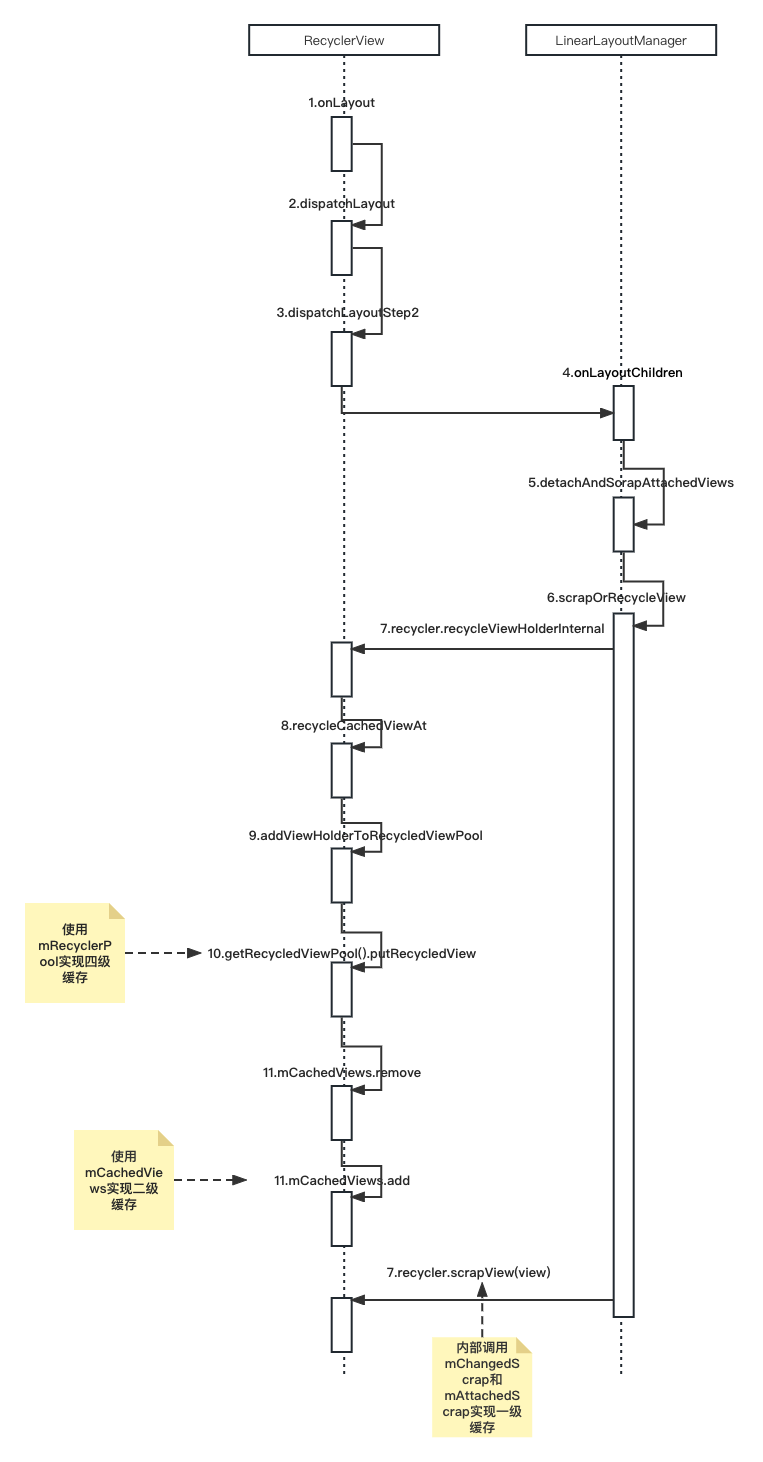

深入源码分析RecyclerView缓存复用原理

文章目录 前言四级缓存 源码分析缓存一级缓存(mChangedScrap和mChangedScrap)二级缓存(mCachedViews)三级缓存(ViewCacheExtension)四级缓存(mRecyclerPool)缓存池mRecyclerPool结构…...

内网隧道代理技术(一)之内网隧道代理概述

内网隧道代理技术 内网转发 在渗透测试中,当我们获得了外网服务器(如web服务器,ftp服务器,mali服务器等等)的一定权限后发现这台服务器可以直接或者间接的访问内网。此时渗透测试进入后渗透阶段,一般情况…...

设计图形用户界面的原则

1) 一般性原则:界面要具有一致性、常用操作要有快捷方式、 提供简单的错误处理、对操作人员的重要操作要有信息反馈、操作可 逆、设计良好的联机帮助、合理划分并高效地使用显示屏、保证信息 显示方式与数据输入方式的协调一致 2) 颜色的使用:颜色…...

1:操作系统导论

1.1操作系统的定义 •Anoperatingsystemactsanintermediarybetweenuserofacomputerandthecomputer hardware. ◦ 操作系统充当计算机⽤⼾和计算机硬件之间的中介 •Thepurposeofanoperatingsystemistoprovideanenvironmentinwhichausercanexecute programsinaconvenientandeff…...

什么是微软的 Application Framework?

我是荔园微风,作为一名在IT界整整25年的老兵,今天来看一下什么是微软的 Application Framework? 到底什么是 Application Framework? 还没有真正掌握任何一套Application Framework的使用之前,就来研究这个真的不是很…...

一个关于宏定义的问题,我和ChatGPT、NewBing、Google Bard、文心一言 居然全军覆没?

文章目录 一、问题重述二、AI 解题2.1 ChatGPT2.2 NewBing2.3 Google Bard2.4 文心一言2.5 小结 一、问题重述 今天在问答模块回答了一道问题,要睡觉的时候,又去看了一眼,发现回答错了。 问题描述:下面的z的值是多少。 #define…...

【服务器数据恢复】断电导致RAID无法找到存储设备的数据恢复案例

服务器数据恢复环境: HP EVA存储,6块SAS硬盘组建的raid5磁盘阵列。上层操作系统是WINDOWS SERVER。该存储为公司内部文件服务器使用。 服务器故障&分析: 在遭遇两次意外断电后,设备重启时raid提示“无法找到存储设备”。管理员…...

Windows上不可或缺的5款宝藏软件,工作效率拉满!

职场小白与大牛的区别:小白需要耗费大半天琢磨的事情,而大牛可以只花5分钟就能处理。 “牛人”,即拥有过人之处,专业、经验、技术等等,学会灵活运用高效率的工具也是关键的一点。工具找得好,运用得快&#…...

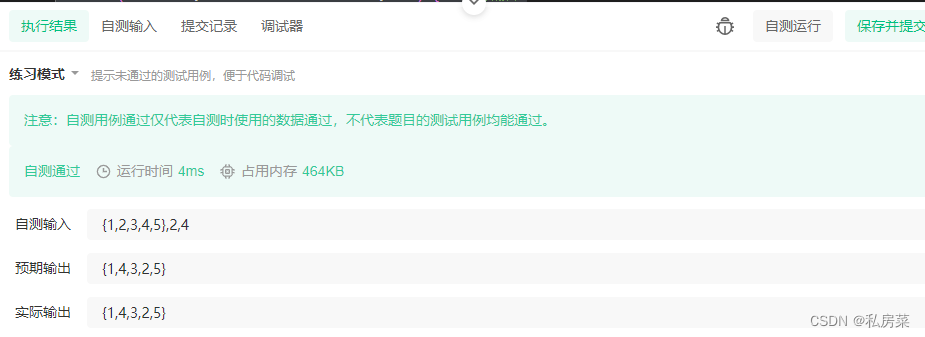

链表内指定区间反转

题目: 将一个节点数为 size 链表 m 位置到 n 位置之间的区间反转,要求时间复杂度 O(n),空间复杂度 O(1)。 例如: 给出的链表为 1→2→3→4→5→NULL,m2,n4 返回 1→4→3→2→5→NULL 数据范围ÿ…...

Vue中如何进行地图展示与交互(如百度地图、高德地图)?

Vue中如何进行地图展示与交互 随着移动互联网的普及,地图应用已经成为人们生活中不可或缺的一部分。在Vue.js中,我们可以使用第三方地图库(如百度地图、高德地图)来实现地图的展示和交互。本文将介绍如何在Vue.js中使用百度地图和…...

uni-app组件概述

1、组件 1.1、组件的含义 组件是视图层的基本组成单元。 组件是一个单独且可复用的功能模块的封装。 组件,包括:以组件名称为标记的开始标签和结束标签、组件内容、组件属性、组件属性值。 <component-name>是开始标签,</compon…...

什么是防火墙?它有什么作用?

作者:Insist-- 个人主页:insist--个人主页 作者会持续更新网络知识和python基础知识,期待你的关注 目录 一、什么是防火墙 二、防火墙的分类 1、软件防火墙 2、硬件防火墙 三、防火墙的作用 1、防止病毒 2、防止访问不安全内容 3、阻…...

基础工程(cubeide串口调试,printf实现,延时函数)

0.基础工程(cubeide串口调试,printf实现,延时函数) 文章目录 0.基础工程(cubeide串口调试,printf实现,延时函数)外部时钟源CLOCK(RCC)系统时钟SYS与DEBUG设置UART串口设置cubeide设置…...

大厂设计师都在用的9个灵感工具

每一件伟大的设计作品都离不开设计师灵感的爆发。设计师有很多灵感来源,比如精美的摄影图片、酷炫的网站设计、APP的特色功能、友好的用户体验动画,或者一篇文章。 设计师每天都需要收集灵感,把灵感收集当成日常生活。在这篇文章中ÿ…...

安全实现SpringBoot配置文件自动加解密

需求背景 应用程序开发的时候,往往会存在一些敏感的配置属性 数据库账号、密码第三方服务账号密码内置加密密码其他的敏感配置 对于安全性要求比较高的公司,往往不允许敏感配置以明文的方式出现。 通常做法是对这些敏感配置进行加密,然后在…...

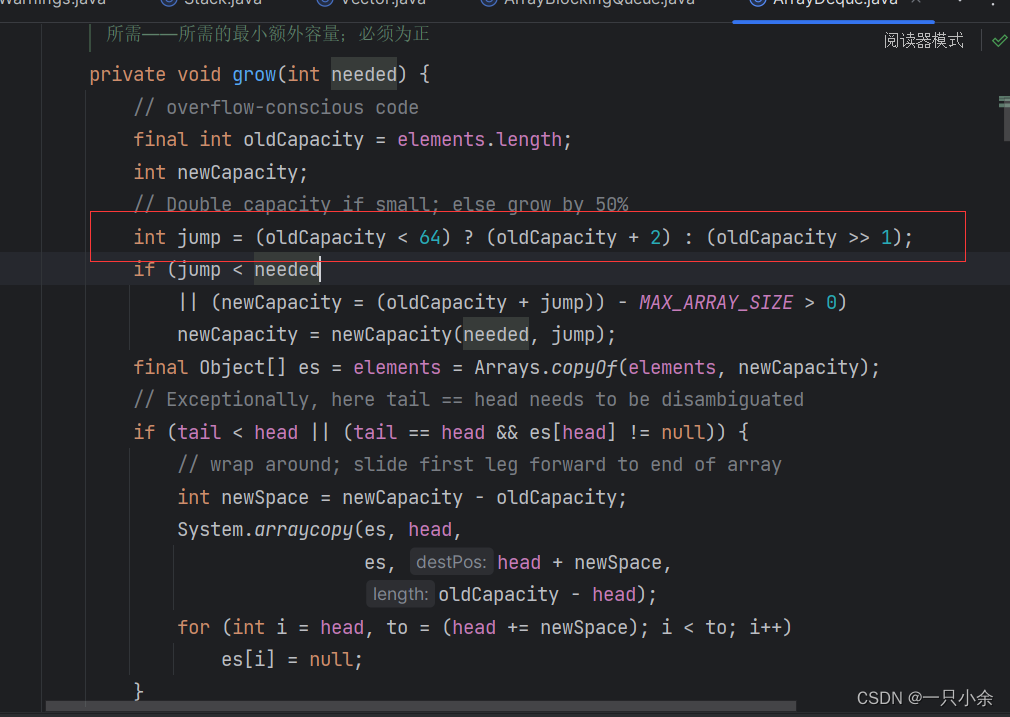

数据结构--队列2--双端队列--java双端队列

介绍 双端队列,和前面学的队列和栈的区别在于双端队列2端都可以进行增删,其他2个都是只能一端可以增/删。 实现 链表 因为2端都需要可以操作所以我们使用双向链表 我们也需要一共头节点 所以节点设置 static class Node<E>{E value;Node<E…...

分布式电池管理系统:基于微控制器架构的智能电池保护与均衡解决方案

分布式电池管理系统:基于微控制器架构的智能电池保护与均衡解决方案 【免费下载链接】SmartBMS Open source Smart Battery Management System 项目地址: https://gitcode.com/gh_mirrors/smar/SmartBMS SmartBMS是一个开源的智能电池管理系统,专…...

OpenClaw自动化测试:百川2-13B驱动的前端元素定位与交互验证

OpenClaw自动化测试:百川2-13B驱动的前端元素定位与交互验证 1. 从手工测试到智能测试的进化之路 作为一名长期奋战在前端测试一线的开发者,我经历过从纯手工点击到Selenium脚本,再到Playwright框架的技术迭代。每次升级都带来效率提升&…...

掌握Nemo文件管理器:Cinnamon桌面环境的高效文件管理利器

掌握Nemo文件管理器:Cinnamon桌面环境的高效文件管理利器 【免费下载链接】nemo File browser for Cinnamon 项目地址: https://gitcode.com/gh_mirrors/ne/nemo Nemo作为Cinnamon桌面环境的默认文件管理器,不仅仅是一个简单的文件浏览器…...

零基础掌握SeleniumBasic:革新性浏览器自动化框架全攻略

零基础掌握SeleniumBasic:革新性浏览器自动化框架全攻略 【免费下载链接】SeleniumBasic A Selenium based browser automation framework for VB.Net, VBA and VBScript 项目地址: https://gitcode.com/gh_mirrors/se/SeleniumBasic 每天重复机械的网页操作…...

WebSocket代理避坑指南:Nginx中proxy_set_header的3个关键配置项

WebSocket代理实战:Nginx中proxy_set_header的3个黄金法则 当在线聊天室的用户突然集体掉线,或是实时协作文档频繁失去同步时,问题往往藏在那些容易被忽视的HTTP头信息里。WebSocket作为现代实时应用的血管,其代理配置的精细程度直…...

)

别再只盯着GNSS了!用移远EC20模组实现基站定位的完整配置流程(含免费Token申请)

移远EC20模组基站定位实战:从零配置到室内场景精准落地 在物联网设备定位领域,GNSS卫星定位长期占据主导地位,但鲜为人知的是,像移远EC20这样的LTE模组还隐藏着一个被低估的功能——基站定位。当你的智能水表安装在地下室、共享设…...

高效安全:从远程服务器到本地Windows的文件传输全攻略

1. 远程桌面连接:最直观的文件传输方式 远程桌面连接(RDP)是Windows系统自带的"杀手级"功能,我帮客户部署项目时90%的场景都会用它传文件。它的优势在于操作可视化程度高,就像直接在服务器桌面上操作本地文件…...

LongCat-Image-Editn部署案例:中小企业低成本AI修图方案,替代Photoshop高频操作

LongCat-Image-Editn部署案例:中小企业低成本AI修图方案,替代Photoshop高频操作 重要提示:本文所有操作均在合规合法的网络环境下进行,所有技术方案均符合相关法律法规要求。 1. 引言:中小企业修图痛点与解决方案 对于…...

终极指南:OpCore Simplify如何让你零基础打造完美黑苹果系统

终极指南:OpCore Simplify如何让你零基础打造完美黑苹果系统 【免费下载链接】OpCore-Simplify A tool designed to simplify the creation of OpenCore EFI 项目地址: https://gitcode.com/GitHub_Trending/op/OpCore-Simplify 还在为复杂的OpenCore EFI配置…...

FOC算法避坑指南:克拉克变换的‘等幅值’与‘等功率’到底选哪个?基于AS5600编码器的实测对比

FOC算法避坑指南:克拉克变换的‘等幅值’与‘等功率’到底选哪个?基于AS5600编码器的实测对比 在无刷电机控制领域,FOC(Field Oriented Control)算法因其优异的动态性能和效率表现,已成为工业驱动和高精度…...